Z8 Microcontrollers

ZiLOG Interrupts

UM001601-0803 7-5

7.4 INTERRUPT INITIALIZATION

After reset, all interrupts are disabled and must be initialized be-

fore vectored or polled interrupt processing can begin. The Inter-

rupt Priority Register (IPR), Interrupt Mask Register (IMR), and

Interrupt Request Register (IRQ) must be initialized, in that or

-

der, to start the interrupt process.

7.4.1 Interrupt Priority Register (IPR) Initializa-

tion

IPR (Figure 7-7) is a write-only register that sets priorities for the

vectored interrupts in order to resolve simultaneous interrupt re

-

quests. (There are 48 sequence possibilities for interrupts.) The

six interrupt levels IRQ0-IRQ5 are divided into three groups of

two interrupt requests each. One group contains IRQ3 and IRQ5.

The second group contains IRQ0 and IRQ2, while the third

group contains IRQ1 and IRQ4.

Priorities can be set both within and between groups as shown in

Tables 7-2 and 7-3. Bits 1, 2, and 5 define the priority of the in

-

dividual members within the three groups. Bits 0, 3, and 4 are en-

coded to define six priority orders between the three groups. Bits

6 and 7 are reserved.

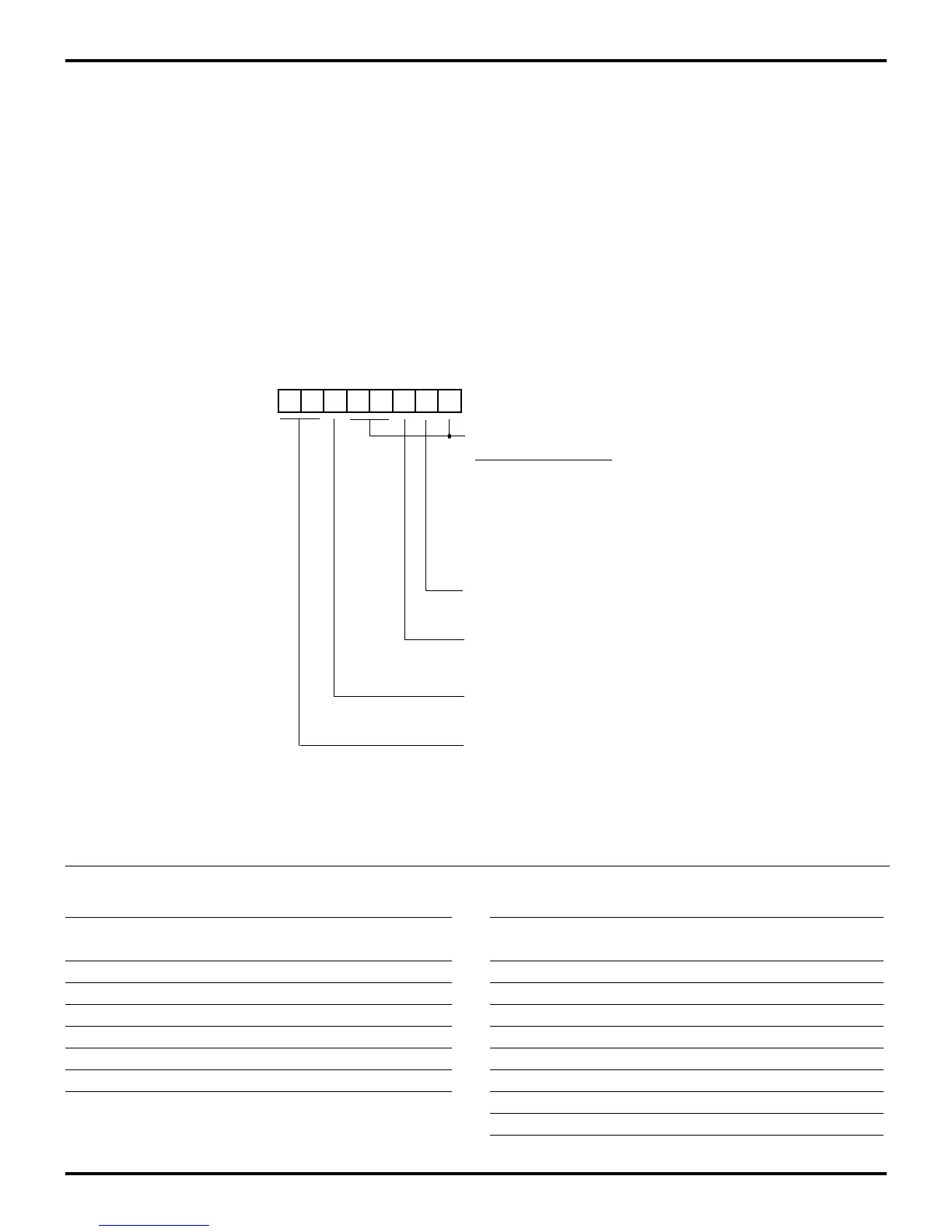

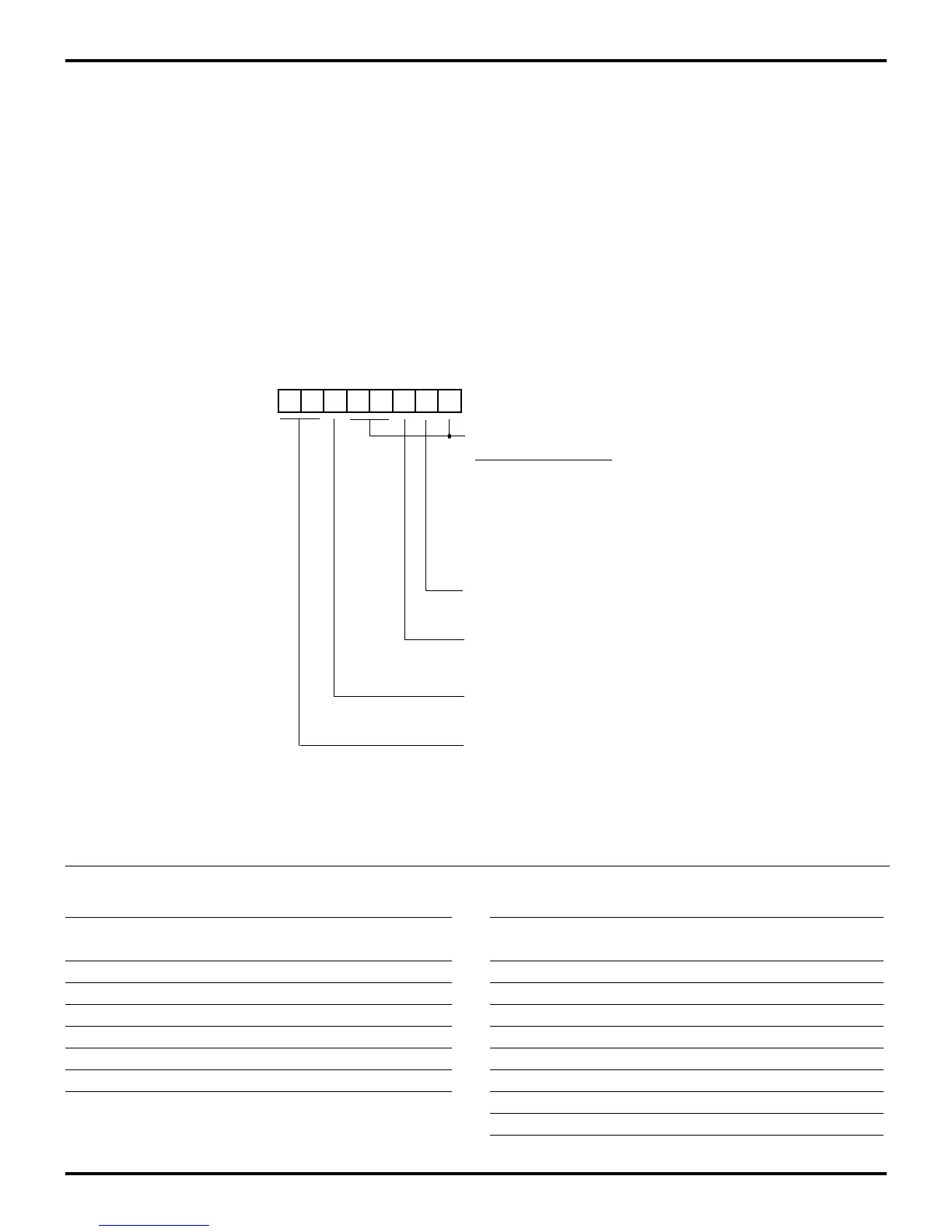

Figure 7-7. Interrupt Priority Register

D7 D6 D5 D4 D3 D2 D1 D0

(Write-Only)

Interrupt Priority Register (IPR)

Register F9H

Interrupt Group Priority

Bits Priority

000 Reserved

001 C > A > B

010 A > B > C

011 A > C > B

100 B > C > A

101 C > B > A

110 B > A > C

111 Reserved

0 = IRQ1 > IRQ4

1 = IRQ4 > IRQ1

Group C (IRQ1 and IRQ4 Priority)

Reserved (Must be 0)

0 = IRQ2 > IRQ0

1 = IRQ0 > IRQ2

Group B (IRQ0 and IRQ2 Priority)

0 = IRQ5 > IRQ3

1 = IRQ3 > IRQ5

Group A (IRQ3 and IRQ5 Priority)

Tab le 7-2. Interrupt Priority

Priority

Group Bit Val ue Highest Lowest

C Bit 1 0 IRQ1 IRQ4

1 IRQ4 IRQ1

B Bit 2 0 IRQ2 IRQ0

1 IRQ0 IRQ2

A Bit 5 0 IRQ5 IRQ3

1 IRQ3 IRQ5

Tab le 7-3. Interrupt Group Priority

Bit Pattern Group Priority

Bit 4 Bit 3 Bit 0 High Medium Low

0 0 0 Not Used

0 0 1 C A B

0 1 0 A B C

0 1 1 A C B

1 0 0 B C A

1 0 1 C B A

1 1 0 B A C

1 1 1 Not Used

Loading...

Loading...