Z8 Microcontrollers

ZiLOG Addressing Modes

UM001601-0803 11-7

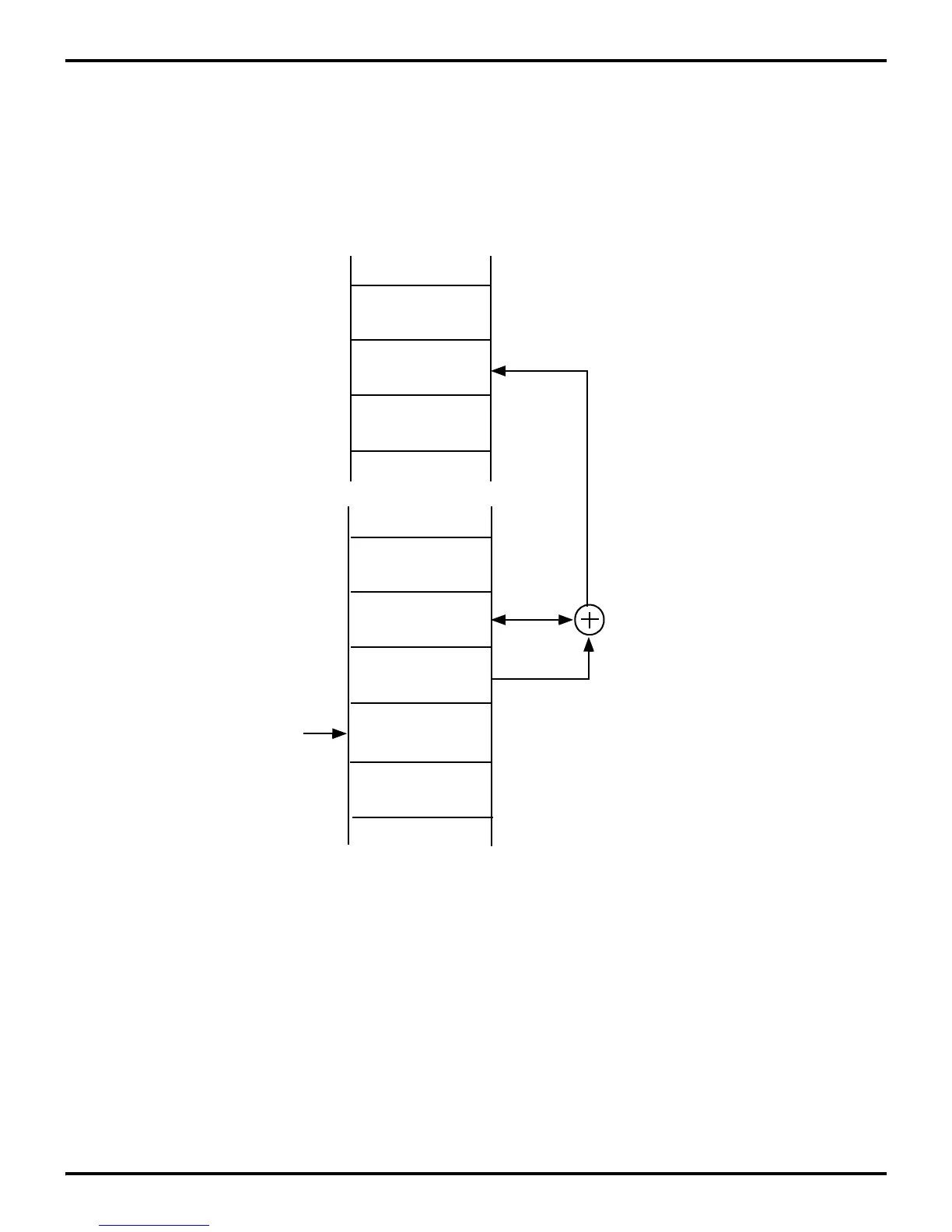

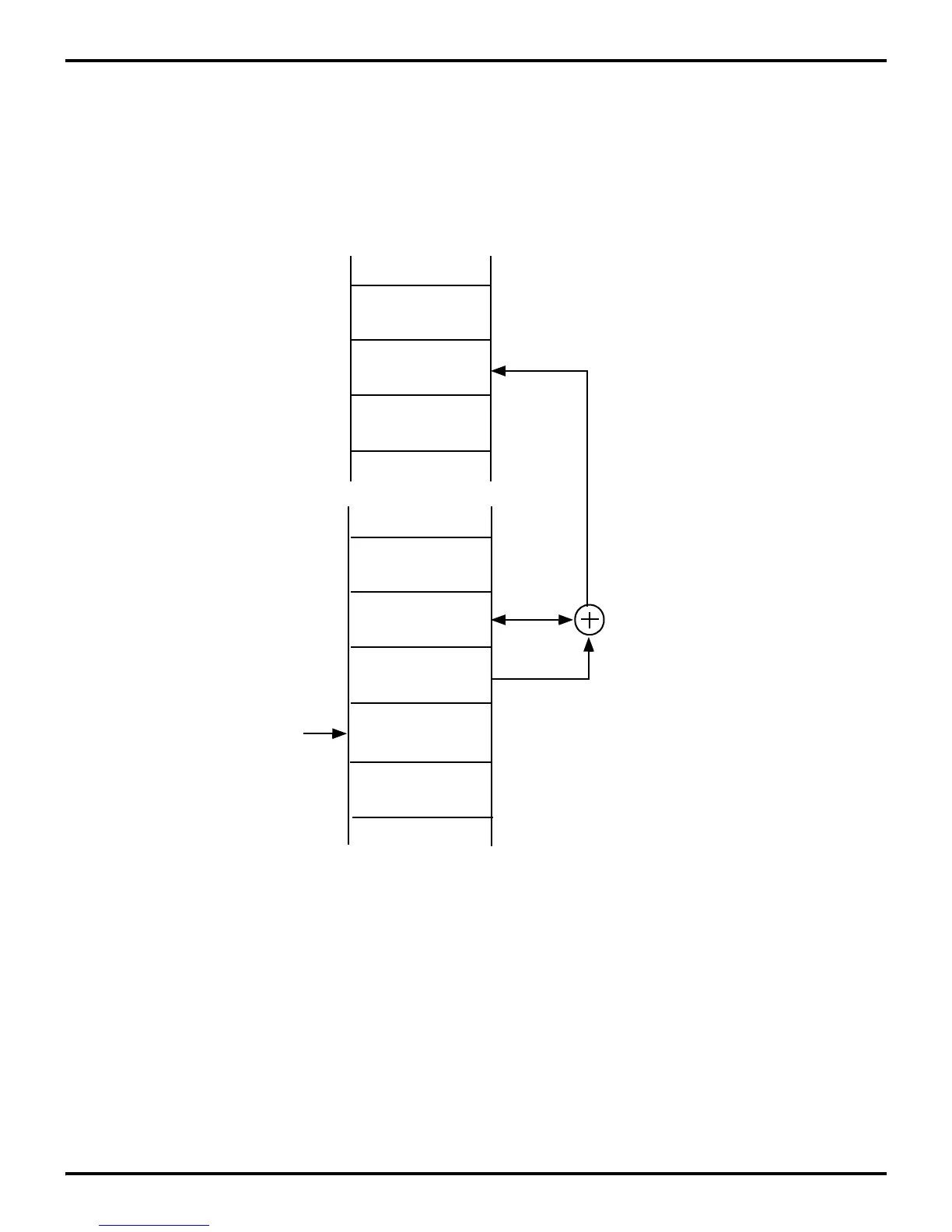

11.6 Z8 RELATIVE ADDRESSING (RA)

In the Relative Addressing mode, illustrated in Figure 11-7, the

instruction specifies a two’s-complement signed displacement in

the range of –128 to +127. This is added to the contents of the

PC to obtain the address of the next instruction to be executed.

The PC (prior to the add) consists of the address of the instruc

-

tion following the Jump Relative (JR) or Decrement and Jump if

Non-Zero (DJNZ) instruction. JR and DJNZ are the only instruc

-

tions which use this addressing mode.

Figure 11-7. Relative Addressing

OpCode

Displacement

Next OpCode

Current

JR or DJNZ

Program Memory

Program Memory

Address Used

PC Value

Loading...

Loading...