Z8 Microcontrollers

External Interface ZiLOG

10-10 UM001601-0803

10.9 Z8 RESET CONDITIONS

After a hardware reset, extended timing is set to accommodate

slow memory access during the configuration routine,

DM is in-

active, the stack resides in the register file. Port 0, 1, and 2 are

reset to input mode. Port 2 is set to Open-Drain Mode.

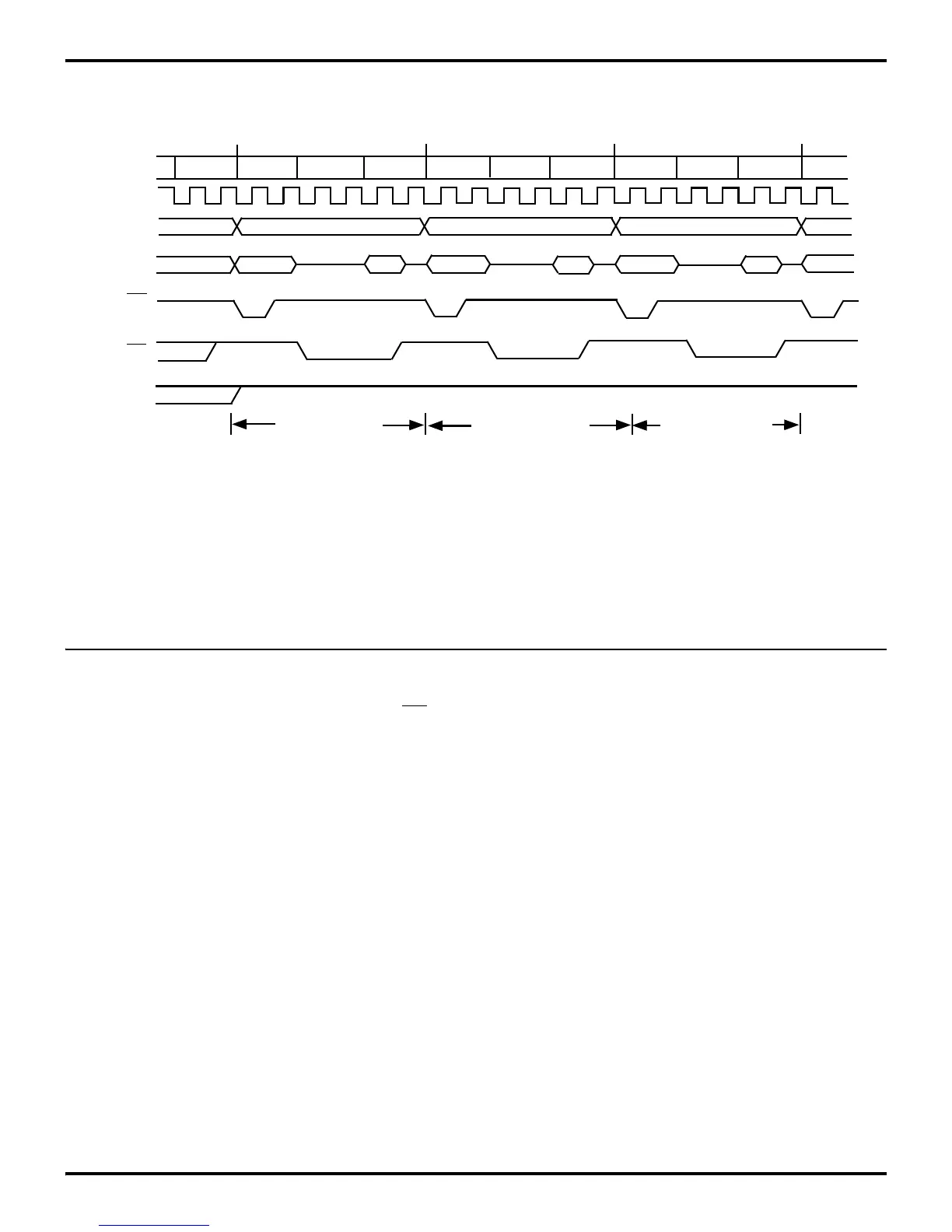

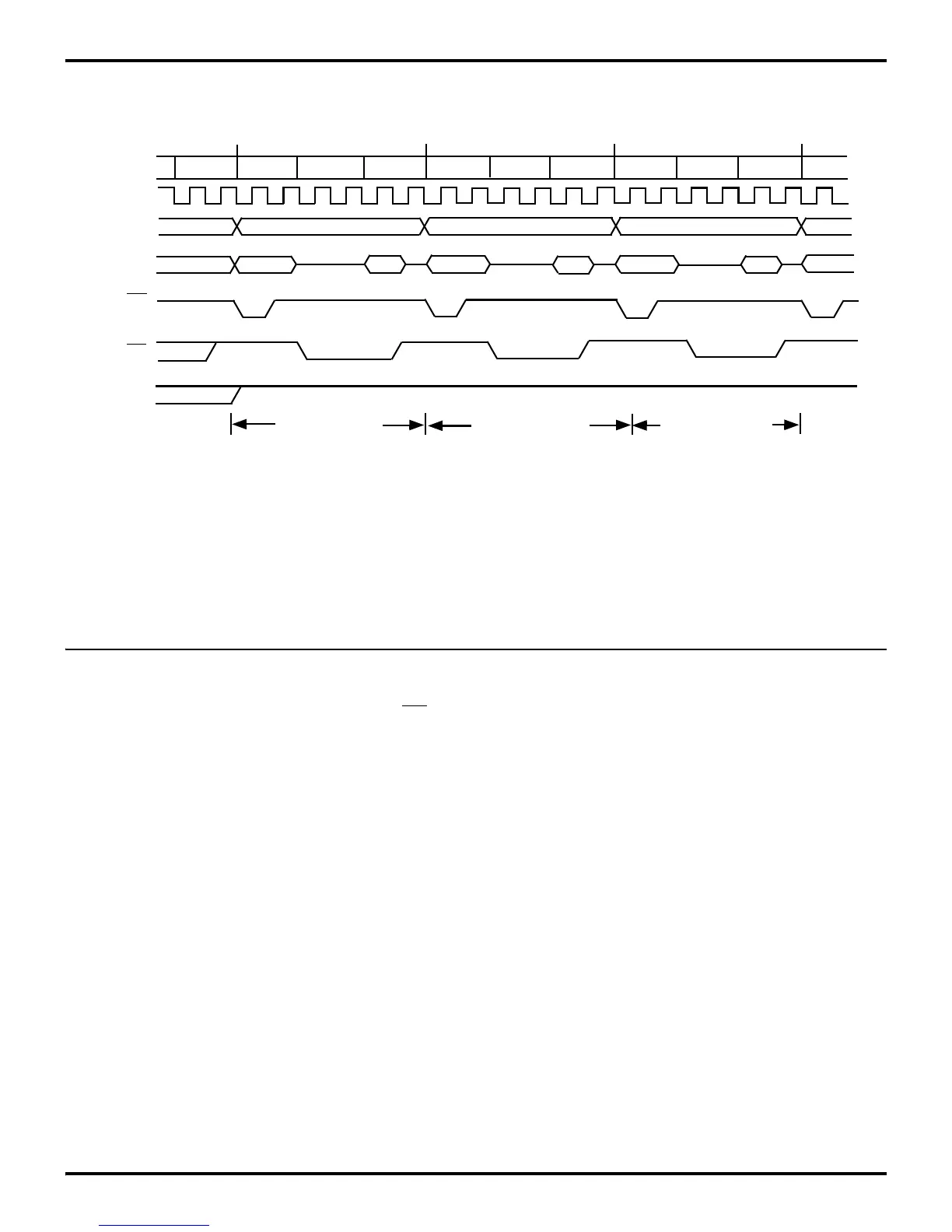

Figure 10-11. Instruction Cycle Timing (2- and 3-Byte Instructions)

T1 T2

T3

T3

T1

DS

AS

R/W

T1

T2

T2

Fetch 1st Byte

T3

M1

M2

M3

A15-A8

A15-A8

A15-A8

A7-A0

A7-A0

A7-A0

A7-A0

A7-A0

Fetch 2nd Byte

Fetch 3rd Byte

Fetch 1st Byte (1- or 2-Byte Instruction)

(3-Byte Instruction)

A15-A8

A7-A0

A7-A0

Clock

*Port inputs are strobed during T2, which is two internal system clocks before

the execution cycle of the current instruction.

Loading...

Loading...