Z8 Microcontrollers

ZiLOG Serial I/O

UM001601-0803 9-11

9.10 RECEIVE CHARACTER AVAILABLE AND OVERRUN

When a complete data stream is received, an interrupt is gener-

ated and the RxCharAvail bit in the SCON Register is set. Bit 4

in the SCON Register is for enabling or disabling the RxCharA

-

vail interrupt. The RxCharAvail bit is available for interrupt

polling purposes and is reset when the RxBUF Register is read.

RxCharAvail is generated in both master and slave modes.

While in slave mode, if the RxBUF is not read before the next

data stream is received and loaded into the RxBUF Register, Re

-

ceive Character Overrun (RxCharOverrun) occurs. Since there is

no need for clock control in slave mode, bit D1 in the SPI Con

-

trol Register is used to log any RxCharOverrun (Figure 9-14 and

Figure 9-15).

No Parameter Min Units

1 DI to SK Setup 10 ns

2 SK to D0 Valid 15 ns

3 SS to SK Setup .5 Tsk ns

4 SS to D0 Valid 15 ns

5 SK to DI Hold Time 10 ns

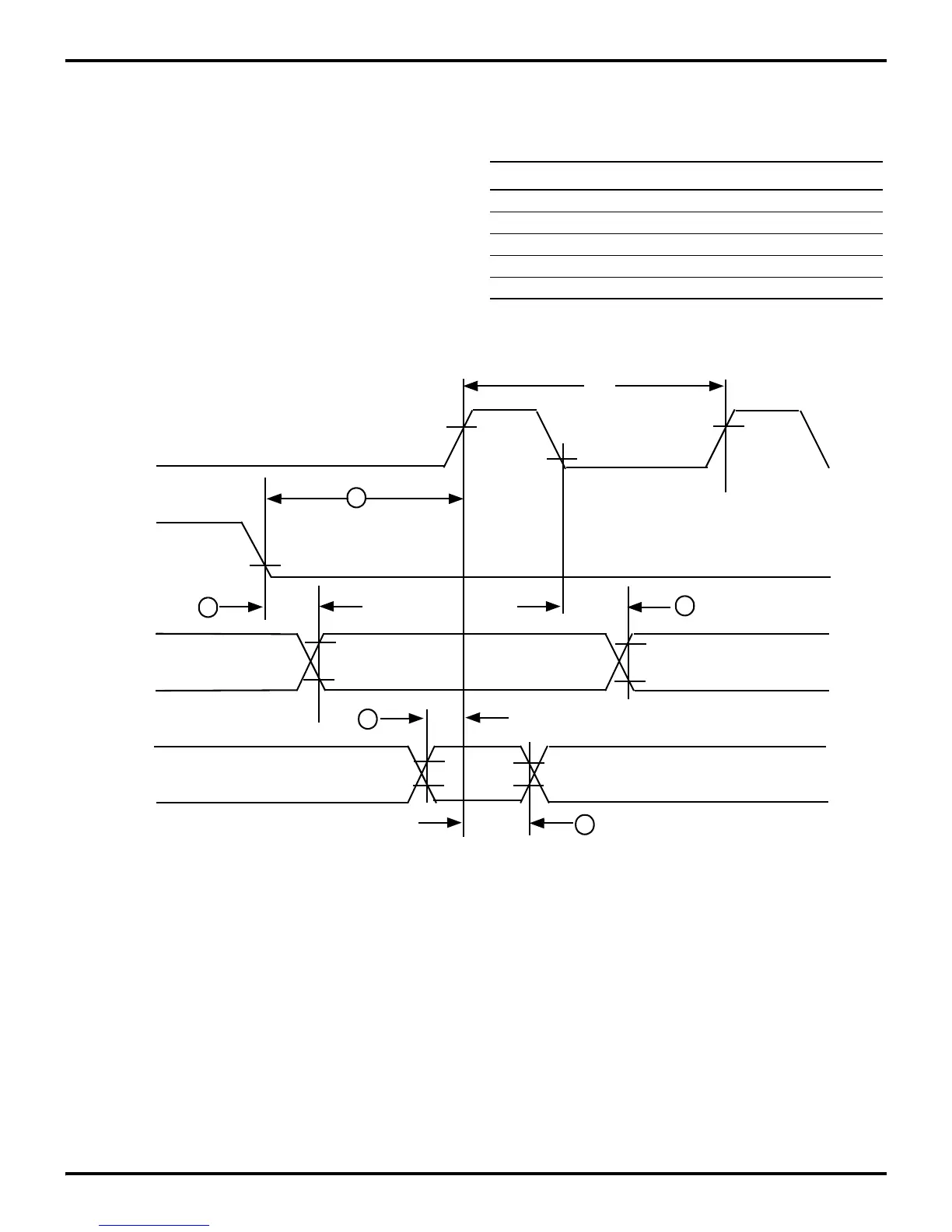

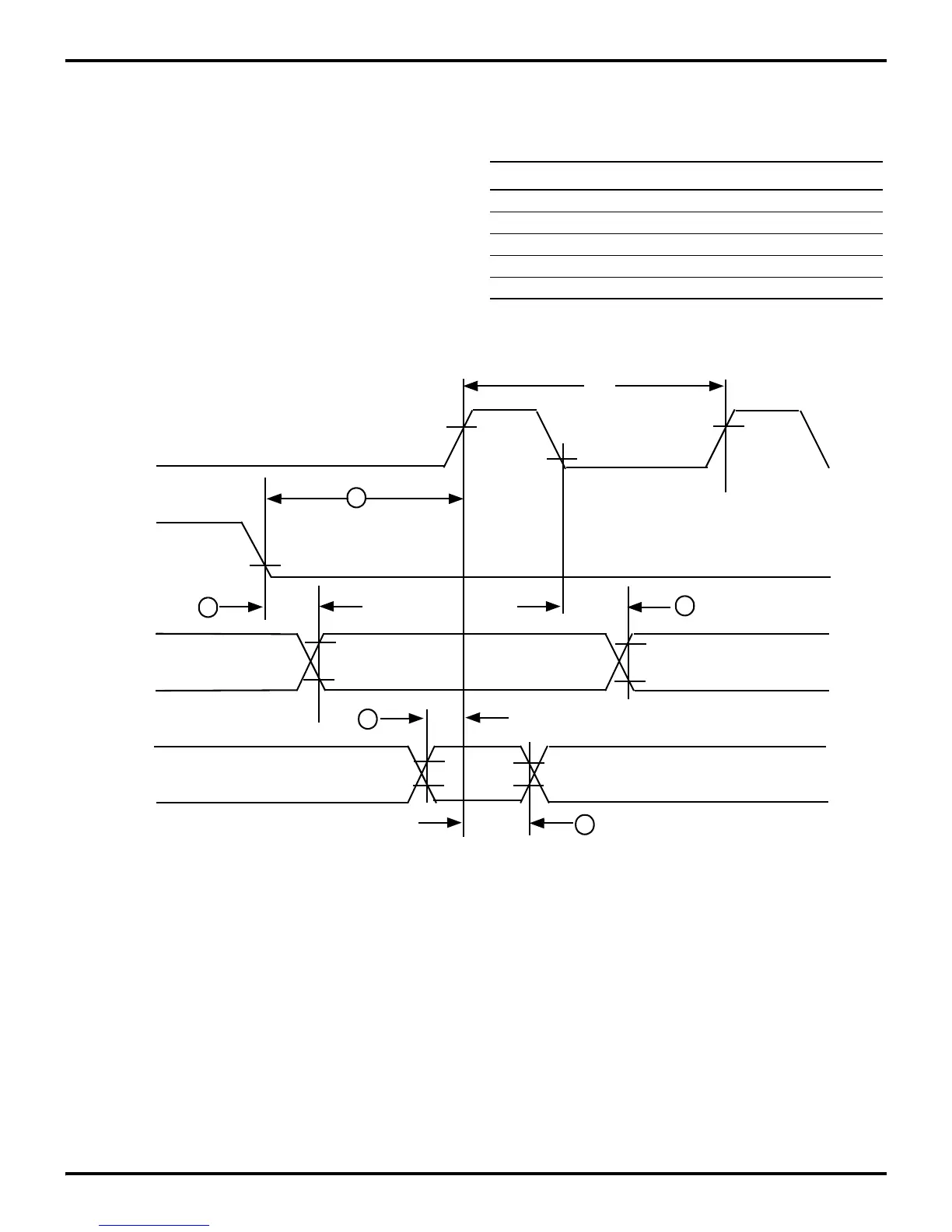

Figure 9-14. SPI Timing

TSK

SS

SK

D0

DI

1

2

3

4

5

Loading...

Loading...