Z8 Microcontrollers

ZiLOG Serial I/O

UM001601-0803 9-7

9.5 UART RESET CONDITIONS

After a hardware reset, the SIO Register contents are undefined,

and Serial Mode and parity are disabled. Figures 9-10 and 9-11

show the binary reset values of the SIO Register and its associ-

ated mode register P3M.

Figure 9-10. SIO Register Reset

U U U U U U U U

(Read/Write)

Serial Data (D

0

= LSB)

Serial I/O Register (SIO)

Register RF0H

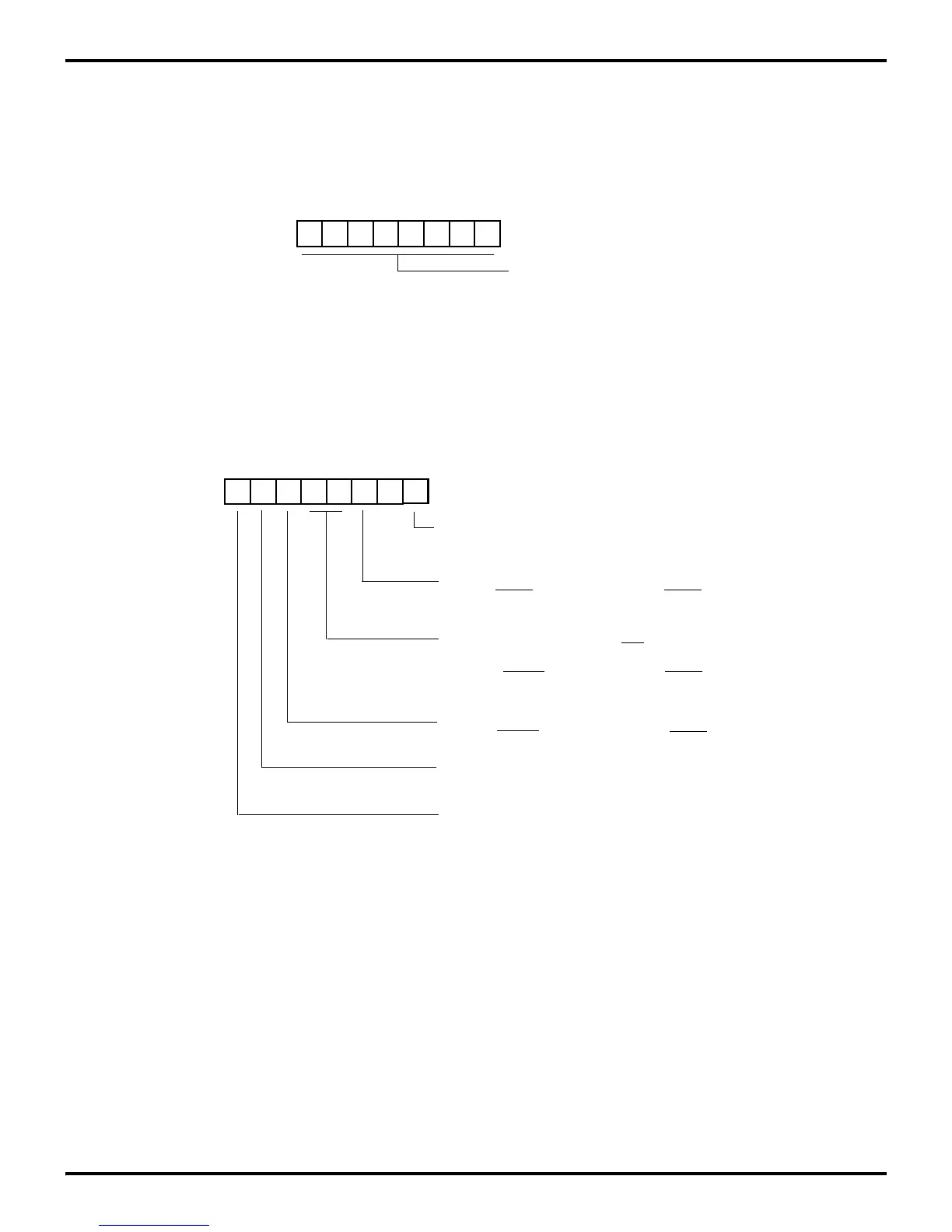

Figure 9-11. P3M Register Reset

0 0 0 0 0 0 0 0

(Write-Only)

0 P32 = Input P35 = Output

1 P32 = DAV0/RDY0 P35 = RDY0/DAV0

0 Port 2 Pull-Ups Open-Drain

1 Port 2 Pull-Ups Active

00 P33 = Input P34 = Output

01 P33 = Input P34 = DM

Port 3 Mode Register (P3M)

Register F7H

10 P33 = Input P34 = DM

11 P33 = DAV1/

RDY1 P34 = RDY1/DAV1

0 P31 = Input (T

IN

) P36 = Output (T

OUT

)

1 P32 =

DAV2/RDY2 P36 = RDY2/DAV2

0 P30 = Input P37 = Output

1 P30 = Serial In P37 = Serial Out

0 Parity ON

1 Parity OFF

Loading...

Loading...