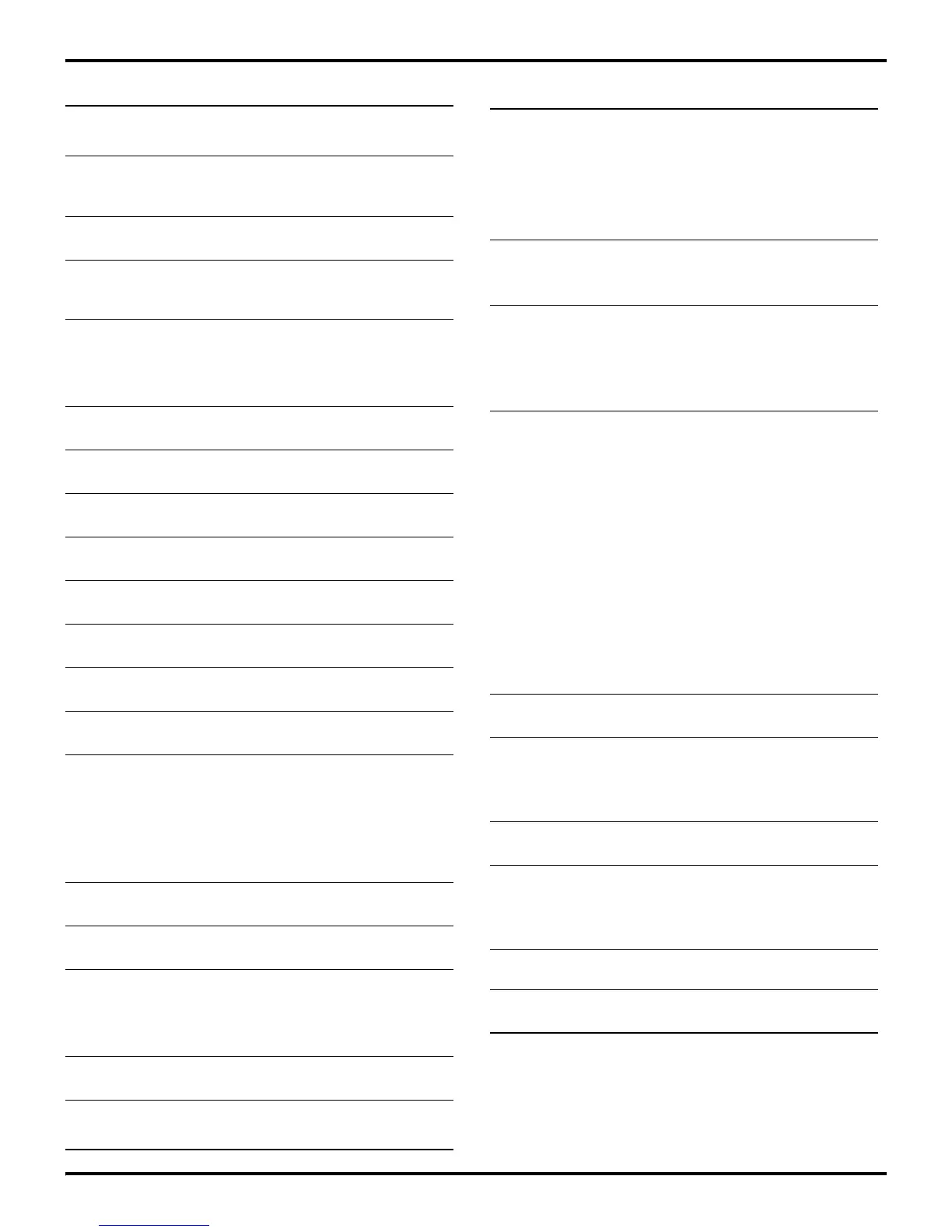

Z8 Microcontrollers

Instruction Set ZiLOG

12-8 UM001601-0803

12.5 Z8 INSTRUCTION SUMMARY

Instruction

and Operation

Address

Mode

Op Code

Byte (Hex)

Flags Affected

dst src C Z S V D H

ADC dst, src

dst ← dst + src

+C

† 1[ ]

✻ ✻ ✻ ✻

0

✻

ADD dst, src

dst ← dst + src

† 0[ ]

✻ ✻ ✻ ✻

0

✻

AND dst, src

dst ← dst AND

src

† 5[ ] –

✻ ✻

0 – –

CALL dst DA D6 – – – – – –

SP ← SP – 2 IRR D4

and PC ← dst

or @ SP ← PC

CCF EF

✻

– – – – –

C ←NOT C

CLR dst R B0 – – – – – –

dst ← 0 IR B1

COM dst R 60 –

✻ ✻

0 – –

dst ← NOT dst IR 61

CP dst, src †

A[ ] ✻ ✻ ✻ ✻

– –

dst − src

DA dst R 40

✻ ✻ ✻

X – –

dst ← DA dst IR 41

DEC dst R 00 –

✻ ✻ ✻

– –

dst ← dst – 1 IR 01

DECW dst R R 80 –

✻ ✻ ✻

– –

dst ← dst – 1 IR 81

DI dst 8 F – – – – – –

IMR(7) ← 0

DJNZr, dst RA rA – – – – – –

r ← r – 1 r=0-F

if r ≠ 0

PC ← PC + dst

Range:+127,

-128

EI 9 F – – – – – –

IMR(7) ← 1

HALT 7 F – – – – – –

INC dst

dst ← dst + 1

r rE –

✻ ✻ ✻

– –

r=0-F

R 20

IR 21

INCW dst RR A0 –

✻ ✻ ✻

– –

dst ← dst + 1 IR A1

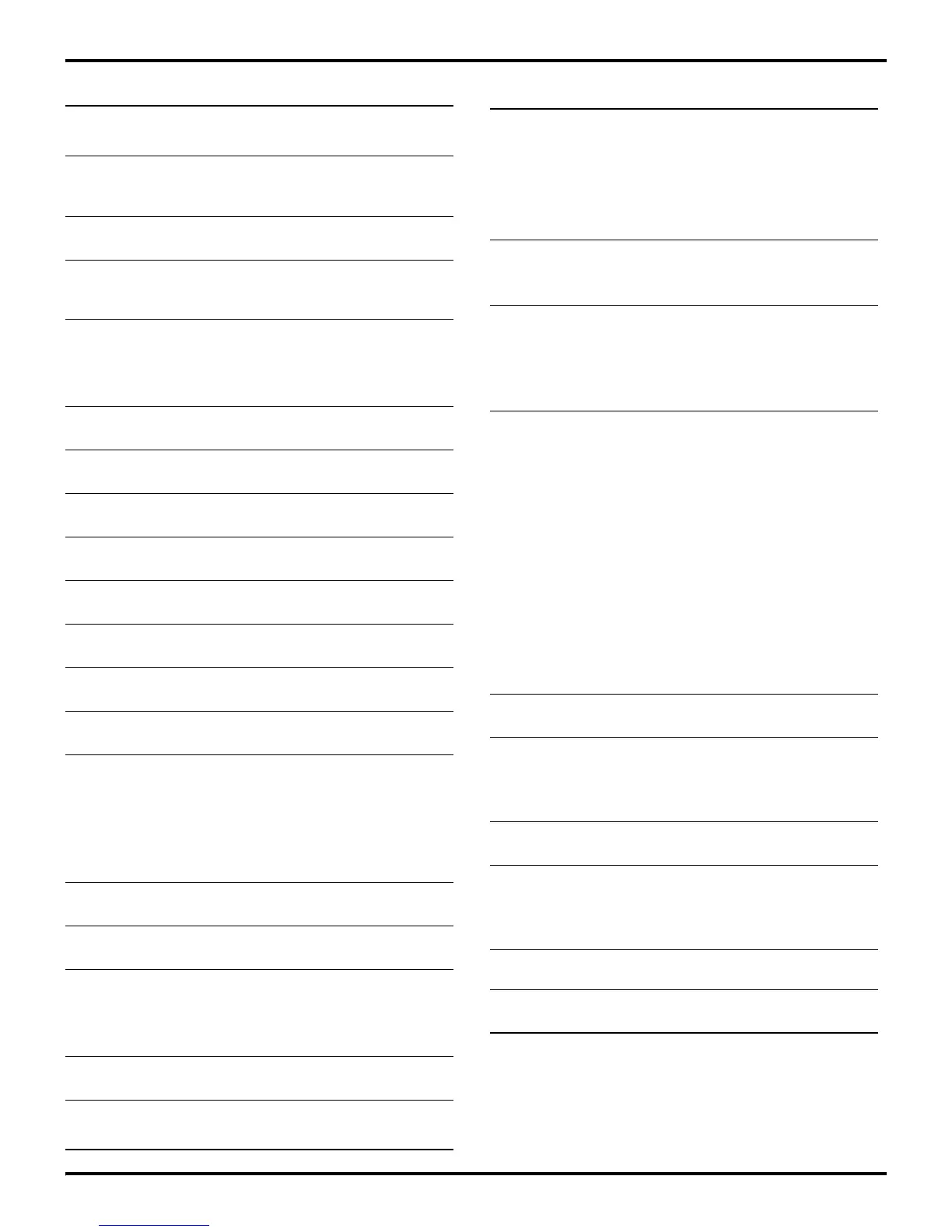

Instruction

and Operation

Address

Mode

Op Code

Byte (Hex)

Flags Affected

dst src C Z S V D H

IRET B F

✻ ✻ ✻ ✻ ✻ ✻

FLAGS←@SP;

SP ← SP + 1

PC ← @SP;

SP ← SP + 2;

and IMR(7) – 1

JP cc, dst DA cD – – – – – –

if cc is true, c = 0 – F

then PC ← dst IRR 30

JR cc, dst RA cB – – – – – –

if cc is true, c = 0 – F

PC ← PC + dst

Range: +127,

–128

LD dst, src r Im r C – – – – – –

dst ← src r R r 8

R r r 9

r = 0 – F

r X C 7

X r D 7

r Ir E 3

Ir r F 3

R R E 4

R IR E 5

R IM E 6

IR IM E 7

IR R F 5

LDC dst, src r Irr C 2 – – – – – –

dst ← src lrr r D 2

LDCI dst, src Ir Irr C 3 – – – – – –

dst ← src lrr Ir D 3

r ← r + 1 or

rr ←rr + 1

LDE dst, src r Irr 82 – – – – – –

dst ← src lrr r 92

LDEI dst, src Ir Irr 83 – – – – – –

dst ← src and lrr Ir 93

r ← r + 1 or

rr ←rr + 1

NOP FF – – – – – –

OR dst, src † 4[ ] –

✻ ✻

0 – –

dst ← dst OR src

Loading...

Loading...