Z8 Microcontrollers

ZiLOG Address Space

UM001601-0803 2-5

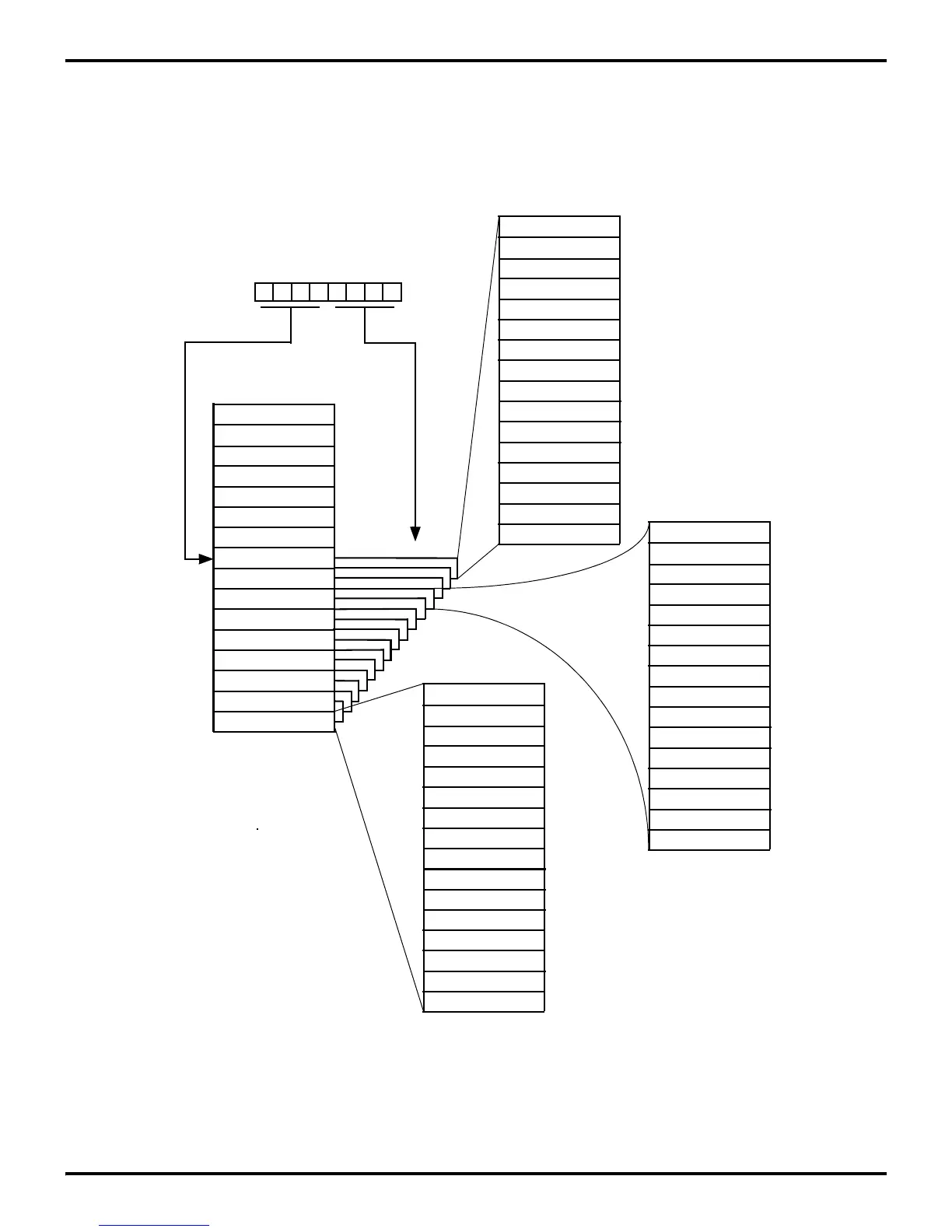

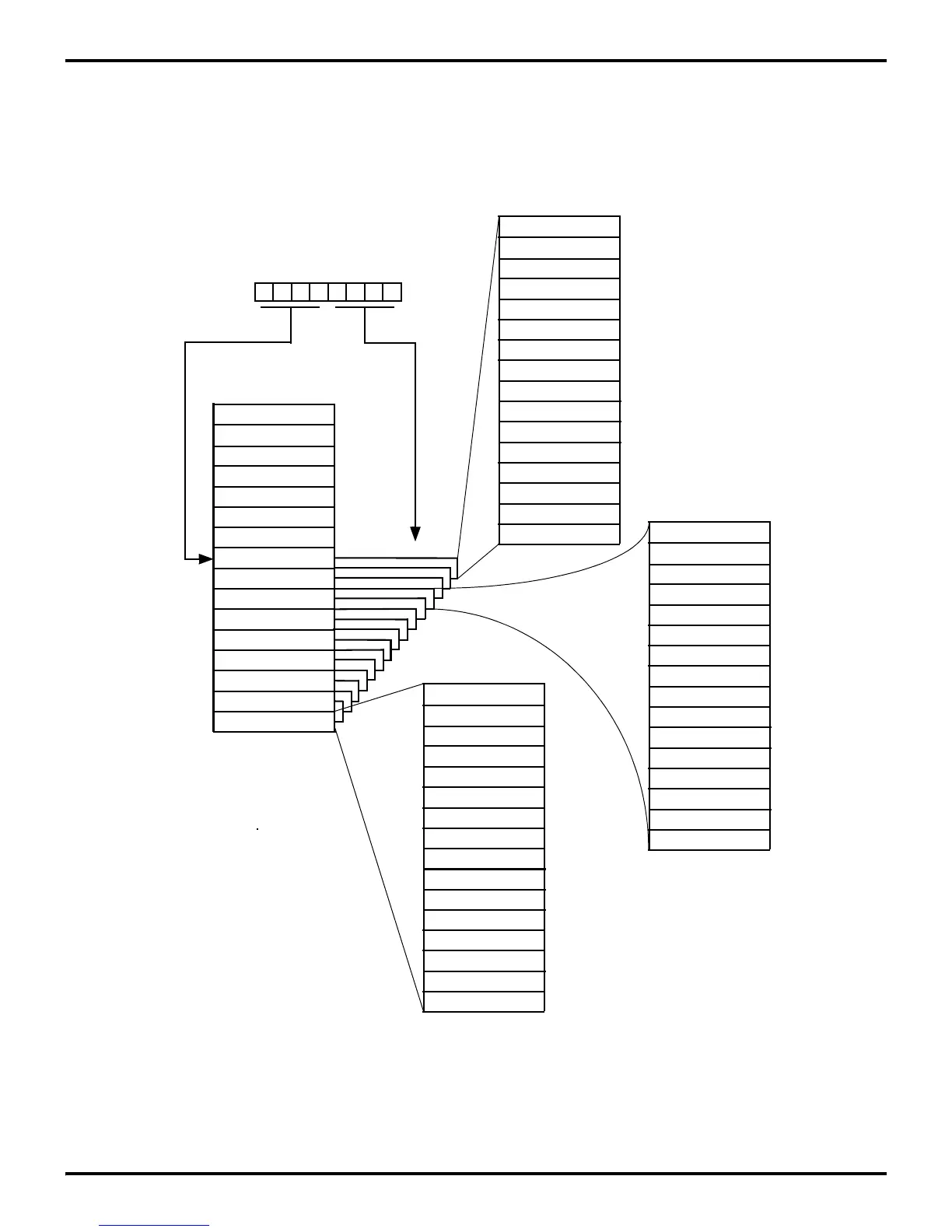

2.3 Z8 EXPANDED REGISTER FILE

The standard register file of the Z8 has been expanded to form

16 Expanded Register File (ERF) Banks (Figure 2-5). Each ERF

Bank consists of up to 256 registers (the same amount as in the

Standard Register File) that can then be divided into 16 Working

Register Groups. This expansion allows for access to additional

feature/peripheral control and data registers.

Note: The fully implemented register file is shown. Please refer to the specific product specification for actual register file architecture implemented.

Currently, three out of the possible sixteen Z8 ERF Banks have

been implemented. ERF Bank 0, also known as the Z8 Standard

Register File, has all 256 bytes defined (Figure 2-1). Only Work-

ing Register Group 0 (register addresses 00H to 0FH) have been

Figure 2-5. Expanded Register File Architecture

Z8 Register File

(F) 0F WDTMR

Expanded Register

FF

0F

7F

F0

00

Expanded Register File

Bank (F)

(F) 0E Reserved

(F) 0D Reserved

(F) 0C Reserved

(F) 0B SMR

(F) 0A Reserved

(F) 09 Reserved

(F) 08 Reserved

(F) 07 Reserved

(F) 06 Reserved

(F) 05 Reserved

(F) 04 Reserved

(F) 03 Reserved

(F) 0E Reserved

(F) 02 Reserved

(F) 01 Reserved

(F) 00 PCON

(0) 0F GPR

Expanded Register File

Bank (0)

(0) 0E GPR

(0) 0D GPR

(0) 0C GPR

(0) 0B GPR

(0) 0A GPR

(0) 09 GPR

(0) 08 GPR

(0) 07 GPR

(0) 06 GPR

(0) 05 GPR

(0) 04 GPR

(0) 03 P3

(0) 02 P2

(0) 01 P1

(0) 00 P0

(C) 0F Reserved

Expanded Register File

Bank (C)

(C) 0E Reserved

(C) 0D Reserved

(C) 0C Reserved

(C) 0B Reserved

(C) 0A Reserved

(C) 09 Reserved

(C) 08 Reserved

(C) 07 Reserved

(C) 06 Reserved

(C) 05 Reserved

(C) 04 Reserved

(C) 03 Reserved

(C) 02 SCON

(C) 01 RXBUF

(C) 00 SCOMP

D7 D6 D5 D4 D3 D2 D1 D0

Working Register

Group Pointer

Group Pointer

Register Pointer

Loading...

Loading...