Z8 Microcontrollers

ZiLOG Instruction Descriptions and Formats

UM001601-0803 12-15

AND

Logical AND

AND

Logical AND

AND dst, src

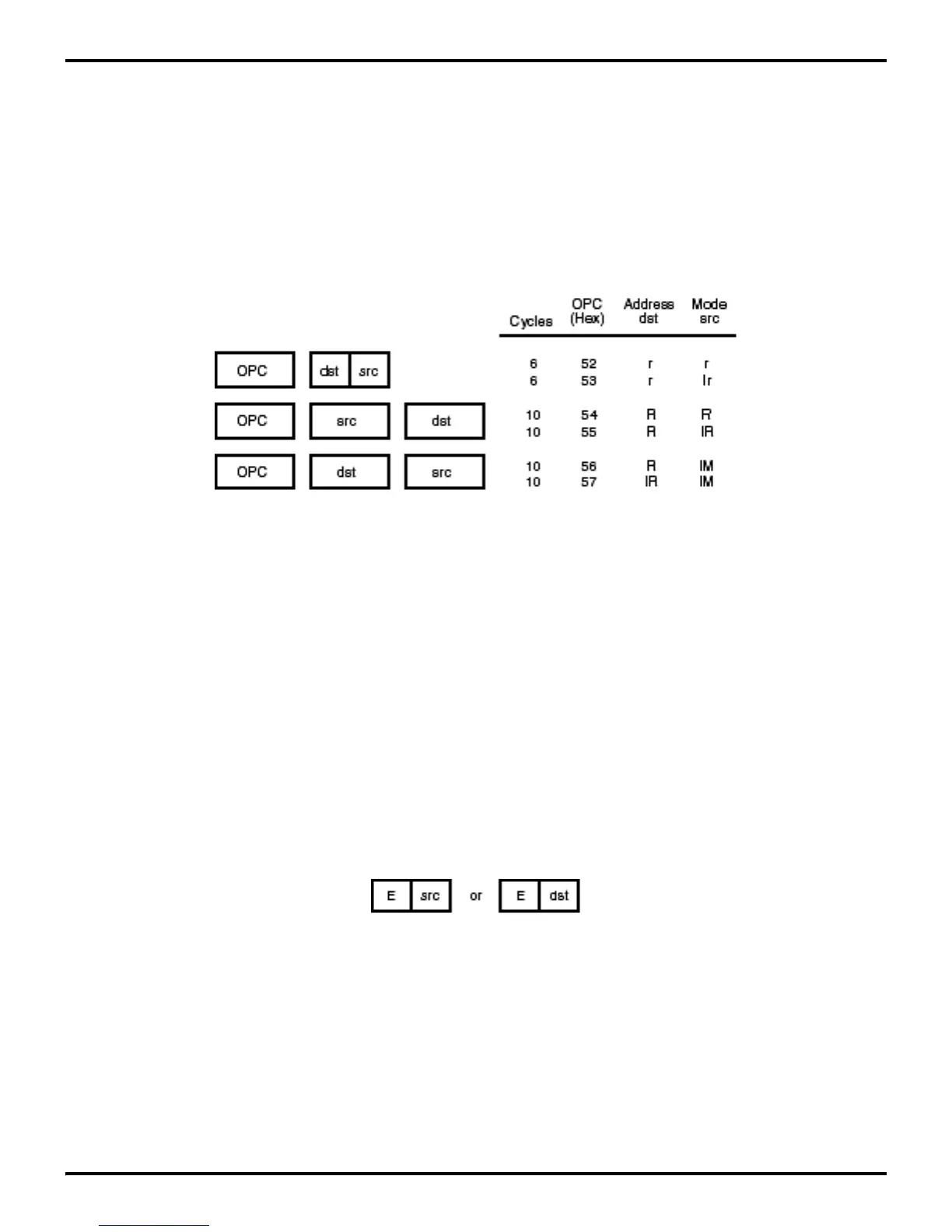

Instruction Format:

Operation:

dst <— dst AND src

The source operand is logically ANDed with the destination operand. The AND operation results in a 1 being stored

whenever the corresponding bits in the two operands are both 1, otherwise a 0 is stored. The result is stored in the

destination operand. The contents of the source bit are not affected.

Note:

Address modes R or IR can be used to specify a 4-bit Working Register. In this format, the source or destination

Working Register operand is specified by adding 1110B (EH) to the high nibble of the operand. For example, if

Working Register R12 (CH) is the destination operand, then ECH will be used as the destination operand in the Op

Code.

Example:

If Working Register R1 contains 34H (00111000B) and Working Register R14 contains 4DH (10001101), the

statement:

AND R1, R14

Op Code: 52 1E

Flags: C: Unaffected

Z: Set if the result is zero; cleared otherwise

S: Set if the result of bit 7 is set; cleared otherwise

V: Always reset to 0

D: Unaffected

H: Unaffected

Loading...

Loading...