A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 104 / 812

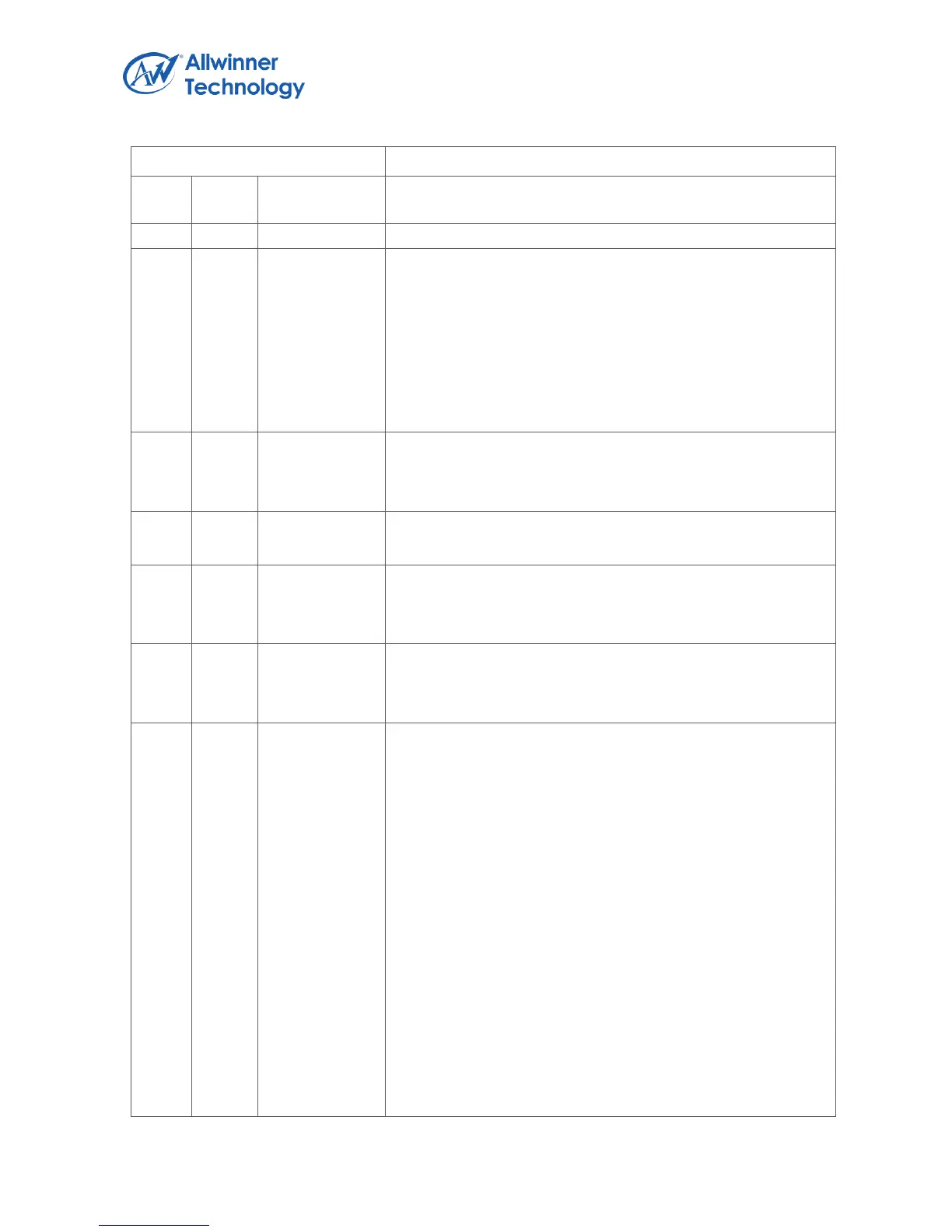

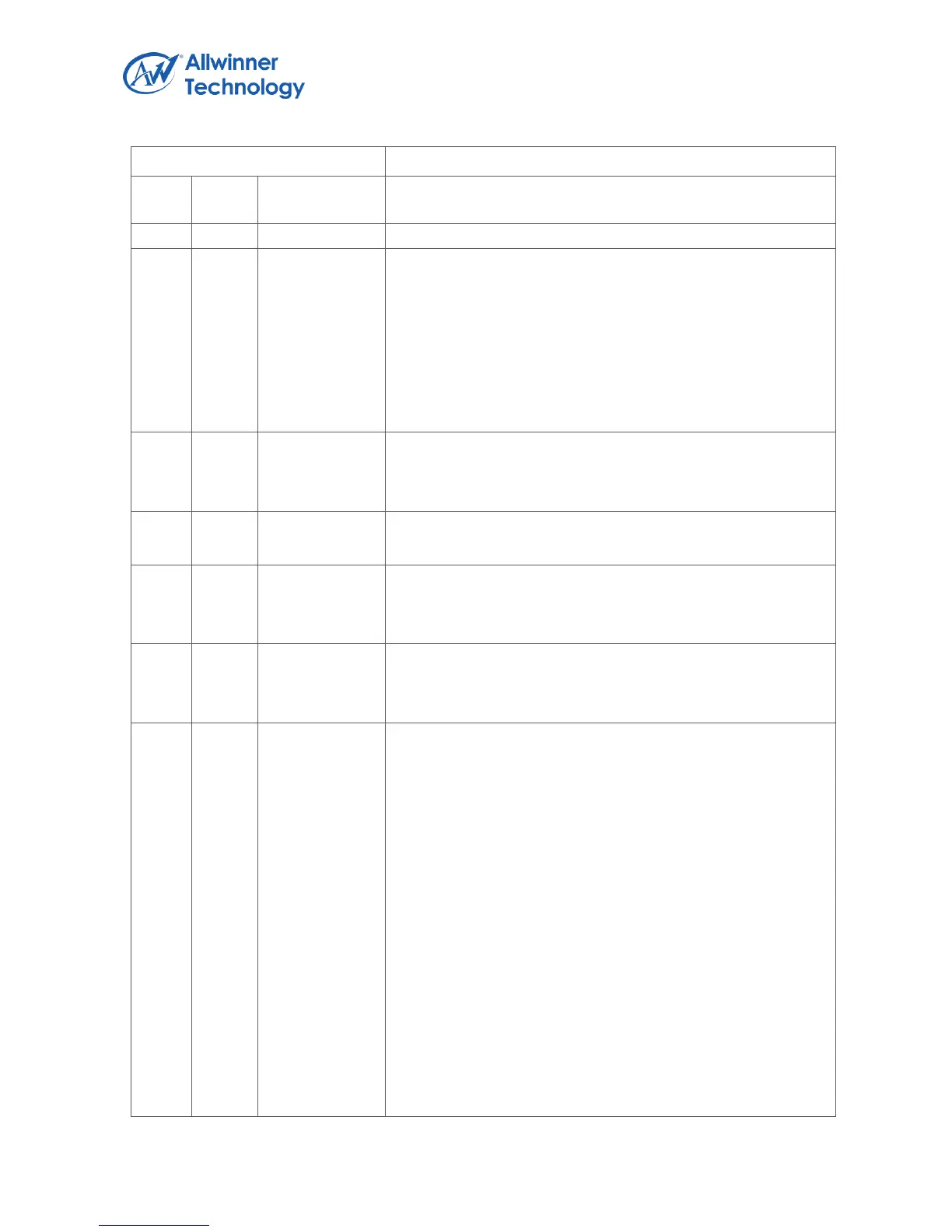

Register Name: PWM_CTRL_REG

PWM_CH1_PULSE_OUT_START.

PWM Channel 1 pulse output start.

0: no effect, 1: output 1 pulse.

The pulse width should be according to the period 1

register[15:0],and the pulse state should be according to the

active state.

After the pulse is finished, the bit will be cleared

automatically.

PWM_CH1_MODE.

PWM Channel 1 mode.

0: cycle mode, 1: pulse mode.

PWM_CH1_CLK_GATING

Gating the Special Clock for PWM1(0: mask, 1: pass).

PWM_CH1_ACT_STATE.

PWM Channel 1 Active State.

0: Low Level, 1: High Level.

PWM_CH1_EN.

PWM Channel 1 Enable.

0: Disable, 1: Enable.

PWM_CH1_PRESCAL.

PWM Channel 1 Prescalar.

These bits should be setting before the PWM Channel 1

clock gate on.

0000: /120

0001: /180

0010: /240

0011: /360

0100: /480

0101: /

0110: /

0111: /

1000: /12k

1001: /24k

1010: /36k

1011: /48k

Loading...

Loading...