A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 120 / 812

1) if the clock source is external CLKIN, the interval value register is not used, the current value

register is an up counter that counting from 0;

2) the time between the timer disabled and enabled should be larger than 2*Tcycles(Tcycles= Timer

clock source/pre-scale).

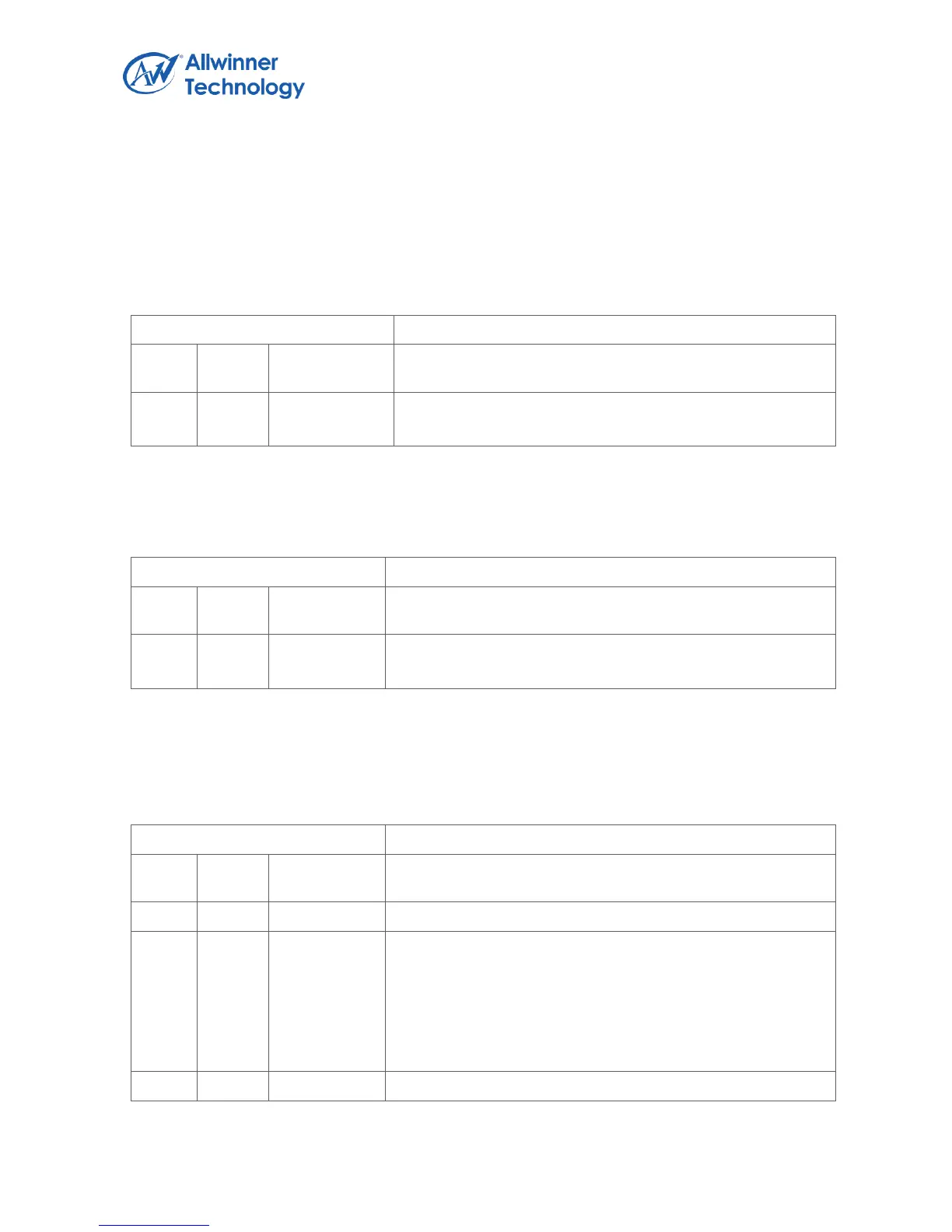

1.9.3.15. TIMER 4 INTERVAL VALUE REGISTER

Register Name: TMR4_INTV_VALUE_REG

TMR4_INTV_VALUE.

Timer 4 Interval Value.

Note: the value setting should take the system clock and the timer clock source into consideration.

1.9.3.16. TIMER 4 CURRENT VALUE REGISTER

Register Name: TMR4_CUR_VALUE_REG

TMR4_CUR_VALUE.

Timer 4 Current Value.

Note:

1) Timer current value is a 32-bit down-counter(from interval value to 0). This register can be read

correctly if the PCLK is faster than 2*TimerFreq(TimerFreq = TimerClkSource/pre-scale);

2) Before the timer 4 is enabled, the timer 4 current value register needs to be written with zero.

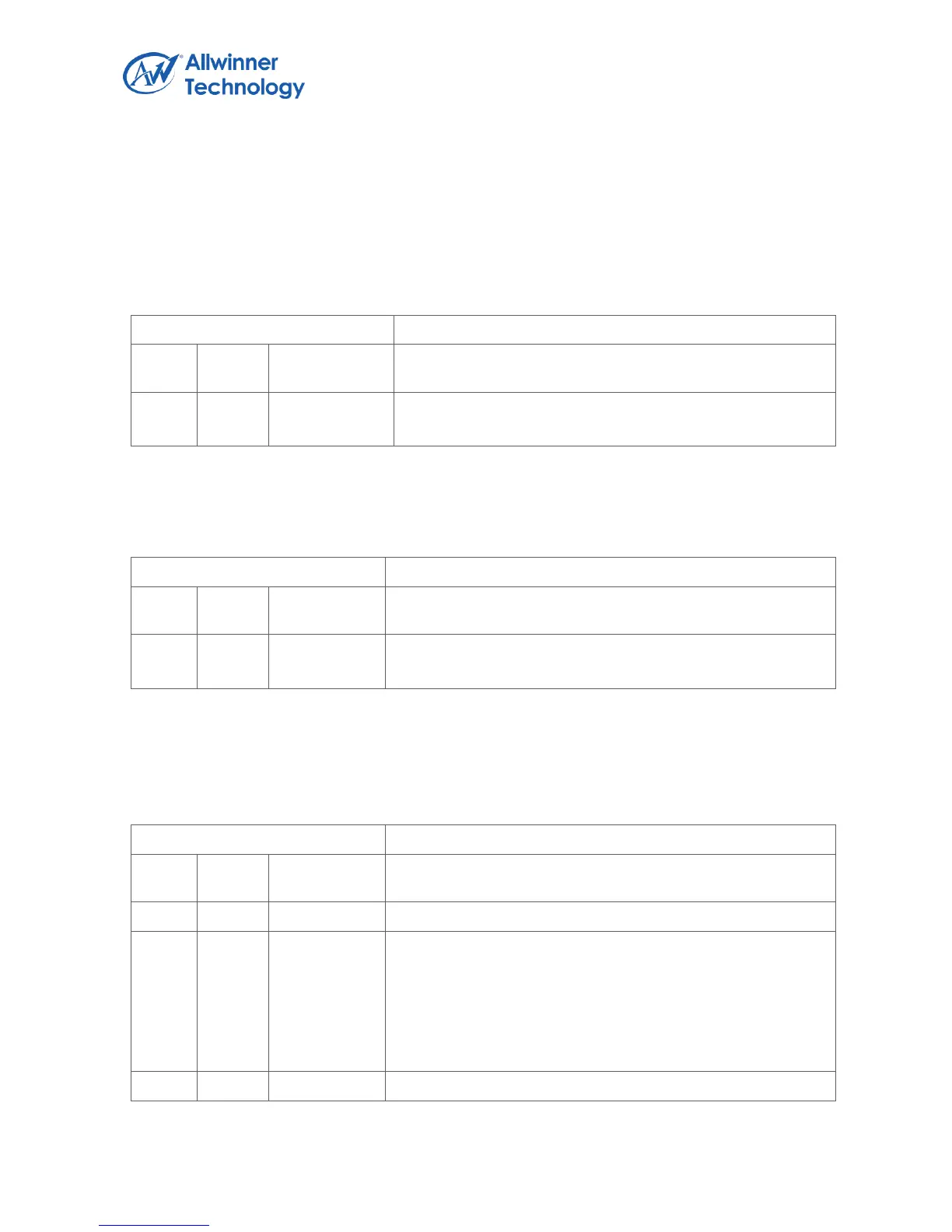

1.9.3.17. TIMER 5 CONTROL REGISTER(DEFAULT: 0X00000004)

Register Name: TMR5_CTRL_REG

TMR5_MODE.

Timer 5 mode.

0: Continuous mode. When interval value reached, the timer

will not disable automatically.

1: Single mode. When interval value reached, the timer will

disable automatically.

Loading...

Loading...