A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 127 / 812

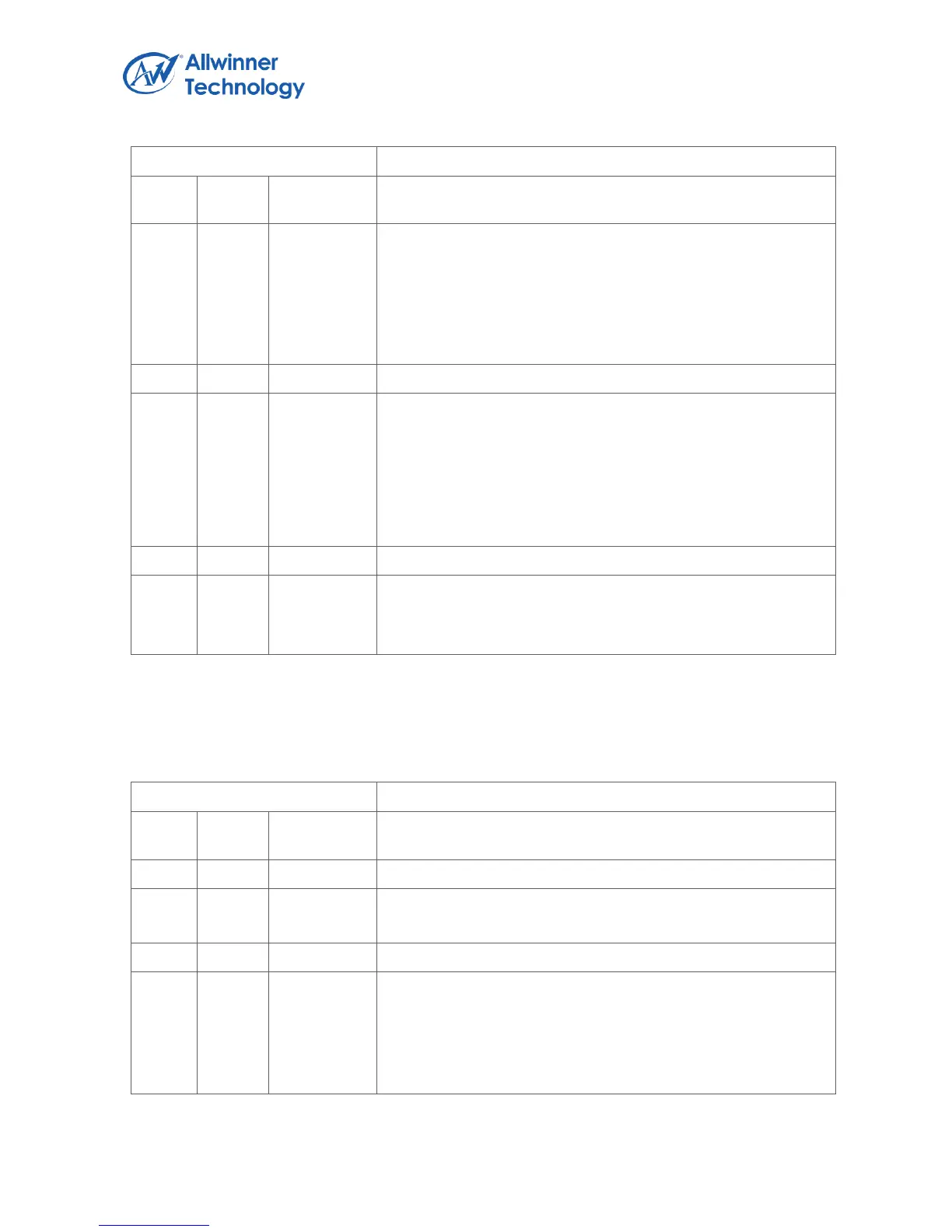

Register Name: LOSC_CTRL_REG

RTC_YYMMDD_ACCE.

RTC YY-MM-DD access.

After writing the RTC YY-MM-DD register, this bit is set and it

will be cleared until the real writing operation is finished.

After writing the RTC YY-MM-DD register, the YY-MM-DD

register will be refreshed for at most one second.

EXT_LOSC_GSM.

External 32768Hz Crystal GSM.

00 low

01

10

11 high

OSC32K_SRC_SEL.

OSC32KHz Clock source Select.

0: Internal 32khz, 1: External 32.768KHz OSC.

Note: If any bit of [9:7] is set, the RTC HH-MM-SS, YY-MM-DD and ALARM DD-HH-MM-SS register

can’t be written.

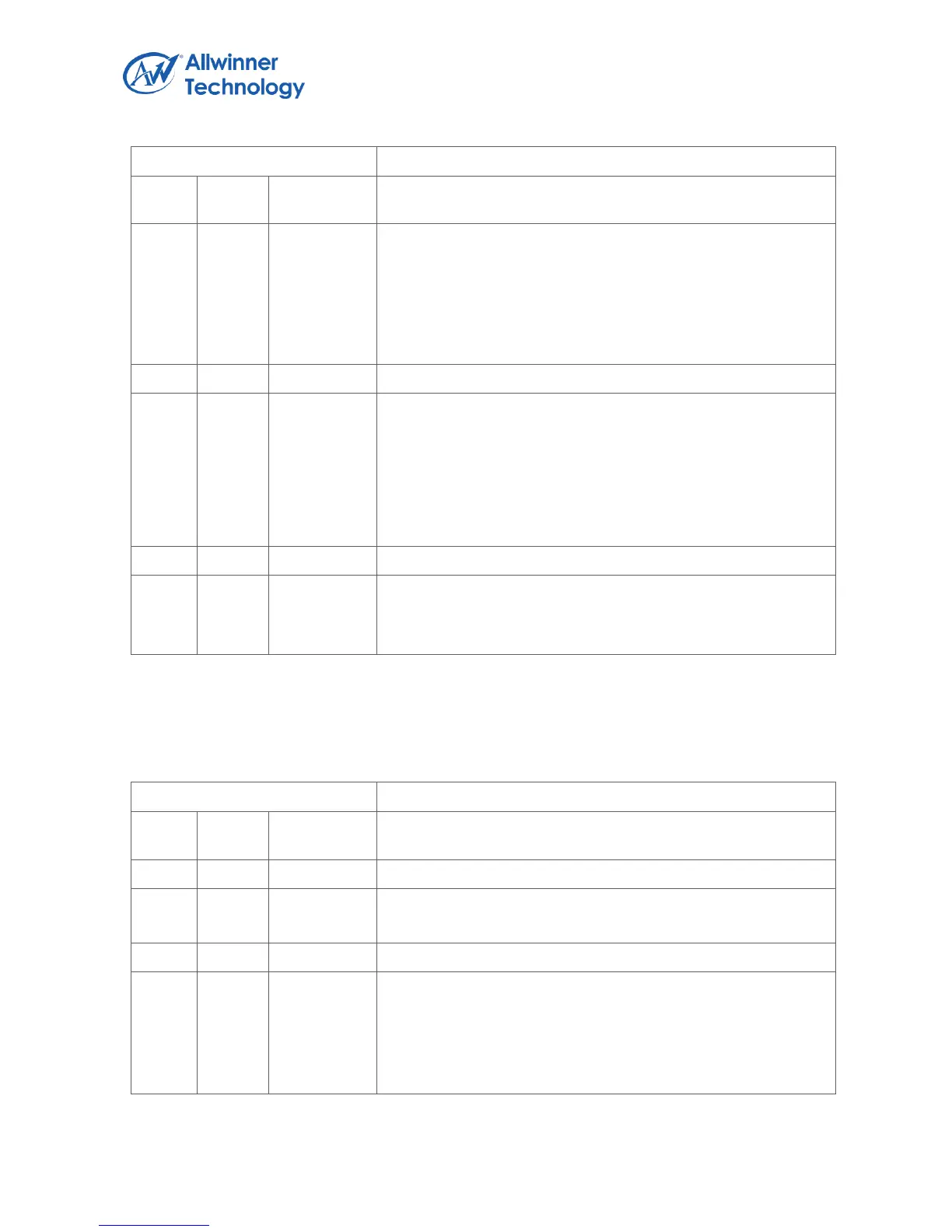

1.9.3.27. RTC YY-MM-DD REGISTER (DEFAULT: 0X00000000)

Register Name: RTC_YY_MM_DD_REG

RTC_SIM_CTRL.

RTC Simulation Control bit.

LEAP.

Leap Year.

0: not, 1: Leap year.

This bit can not set by hardware. It should be set or clear by

software.

Loading...

Loading...