A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 132 / 812

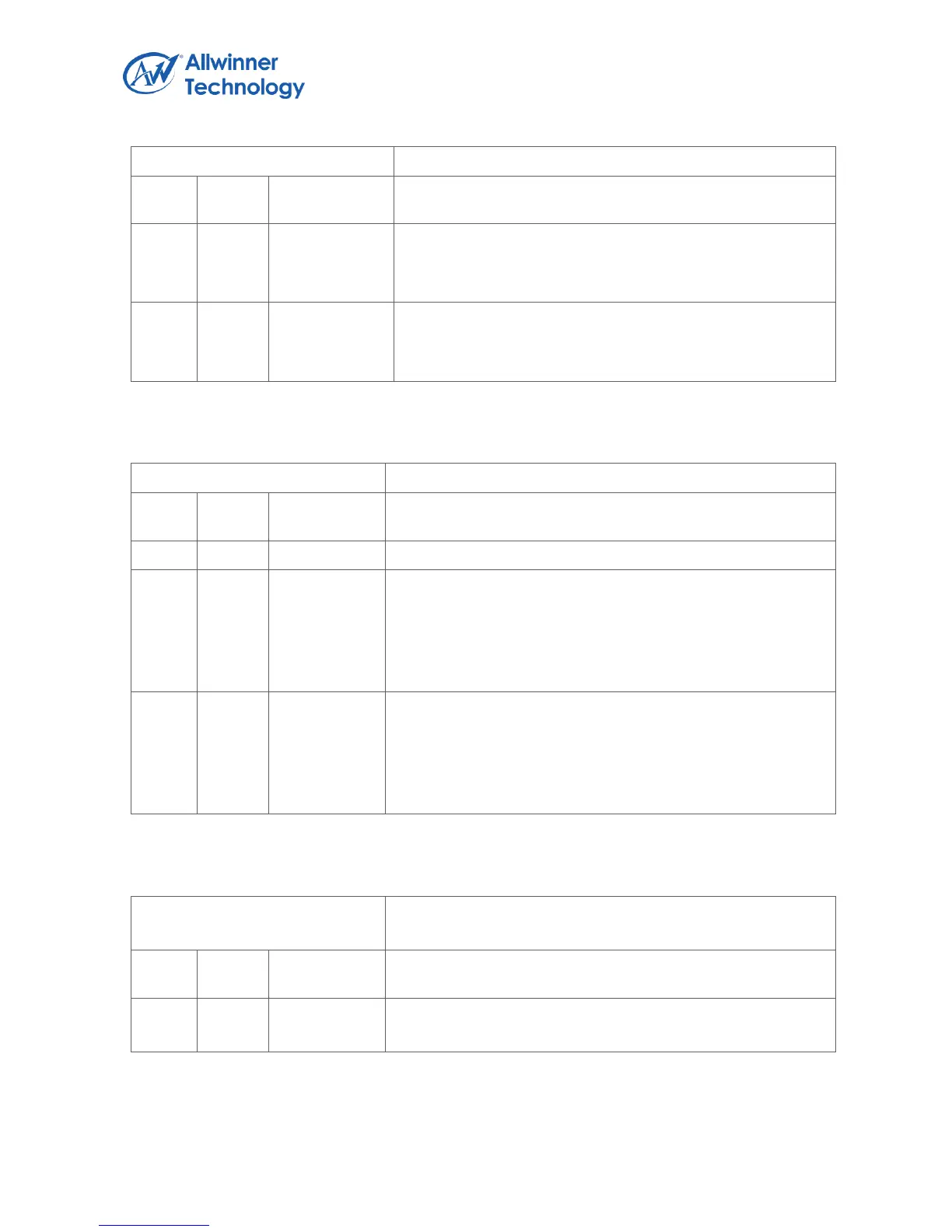

Register Name: ALARM_IRQ_EN

ALARM_WK_IRQ_EN.

Alarm Week IRQ Enable.

0:disable, 1:enable.

ALARM_CNT_IRQ_EN.

Alarm Counter IRQ Enable.

0:disable, 1:enable.

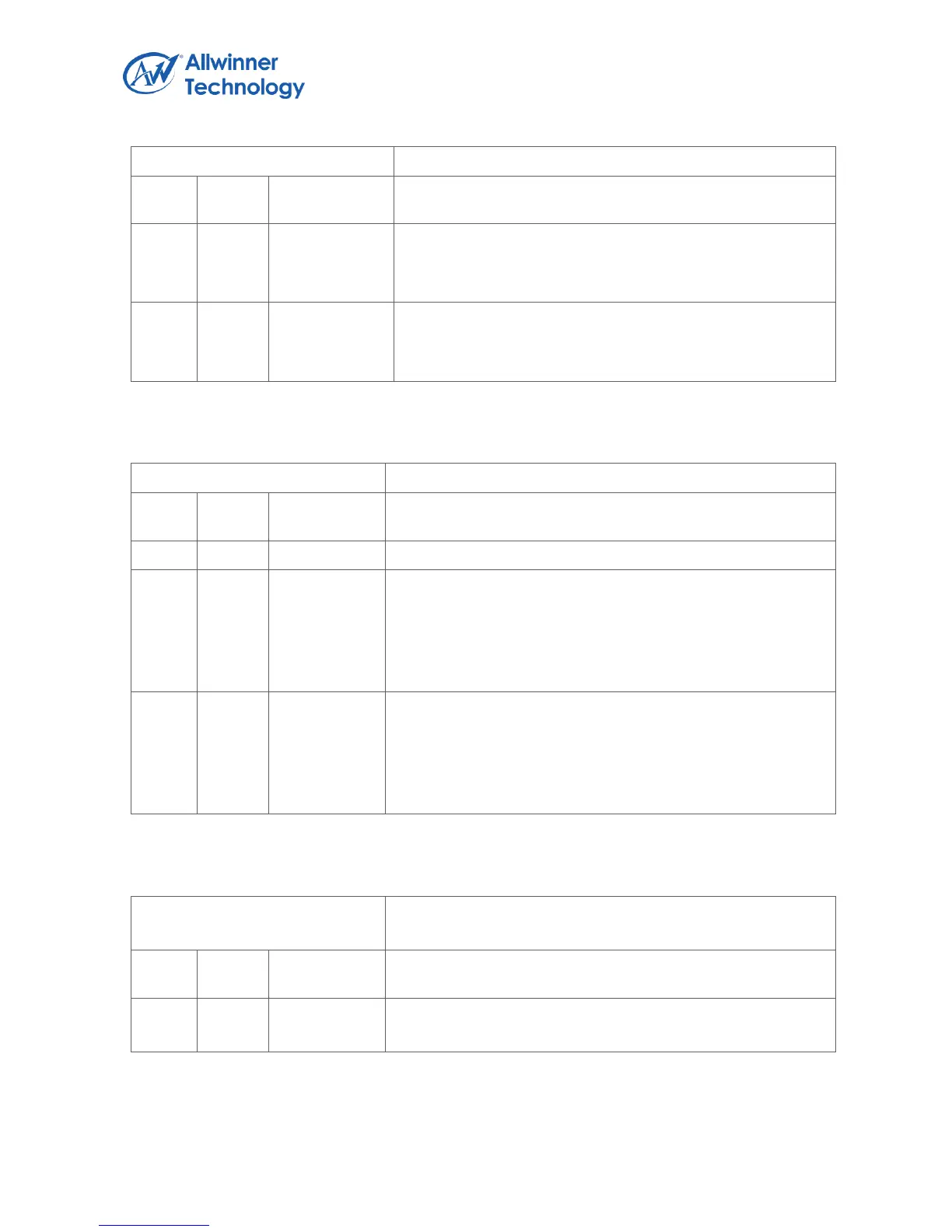

1.9.3.33. ALARM IRQ STATUS REGISTER

Register Name: ALARM_IRQ_STA_REG

WEEK_IRQ_PEND.

Alarm Week (0/1/2/3/4/5/6) IRQ Pending.

0: No effect, 1: Pending, week counter value is reached.

If alarm week irq enable is set to 1, the pending bit will be

sent to the interrupt controller.

CNT_IRQ_PEND.

Alarm Counter IRQ Pending bit.

0: No effect, 1: Pending, alarm counter value is reached.

If alarm counter irq enable is set to 1, the pending bit will be

sent to the interrupt controller.

1.9.3.34. TIMER GENERAL PURPOSE REGISTER

Offset: 0x120+N*0x4

(N=0~15)

Register Name: TMR_GP_DATA_REG

Note: Timer general purpose register value can be stored if the RTCVDD is above 1.0V.

Loading...

Loading...