A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 143 / 812

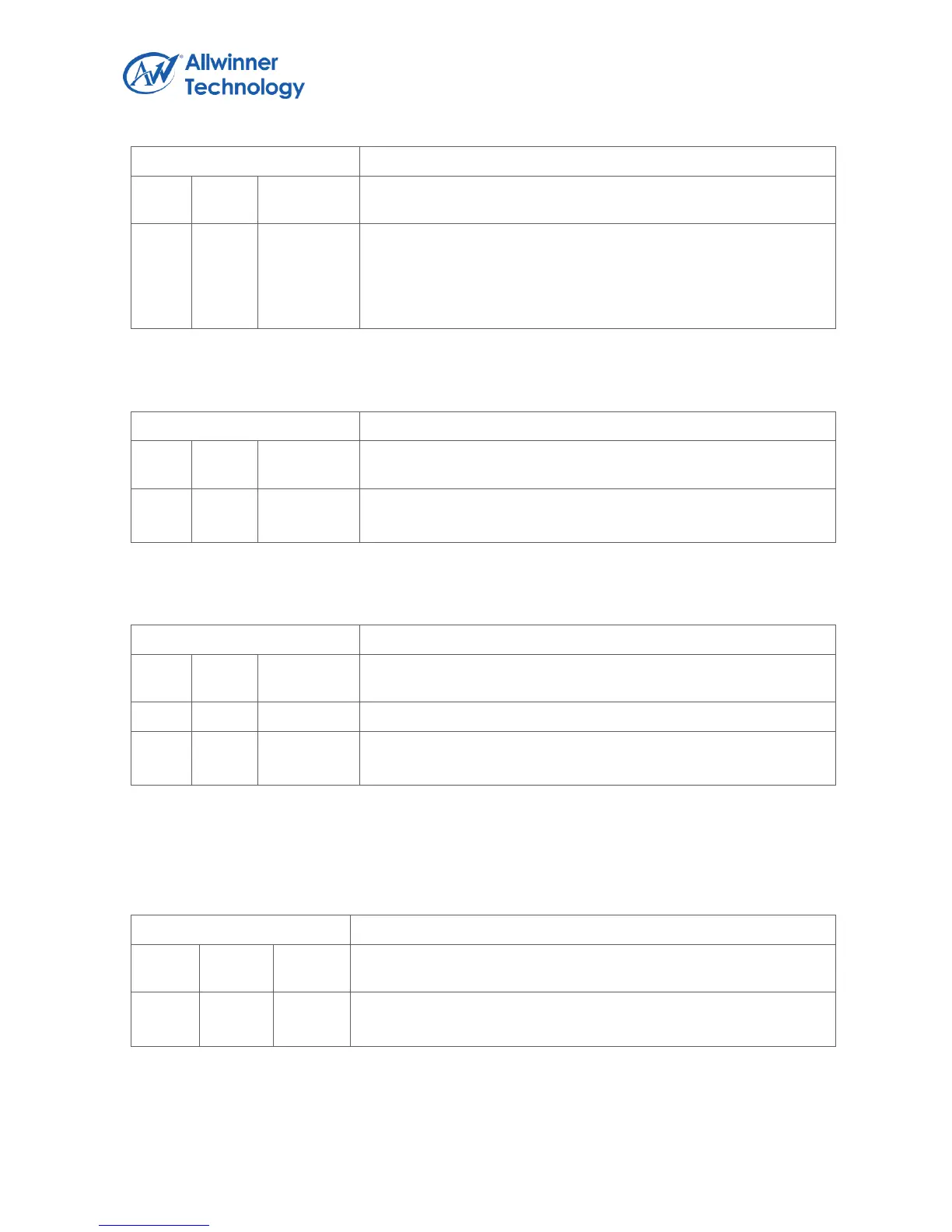

Register Name: HS_TMR2_CTRL_REG

for 2 cycles, the start bit can be set to 1.

In timer pause state, the interval value register can be modified.

If the timer is started again, and the Software hope the current

value register to down-count from the new interval value, the

reload bit and the enable bit should be set to 1 at the same time.

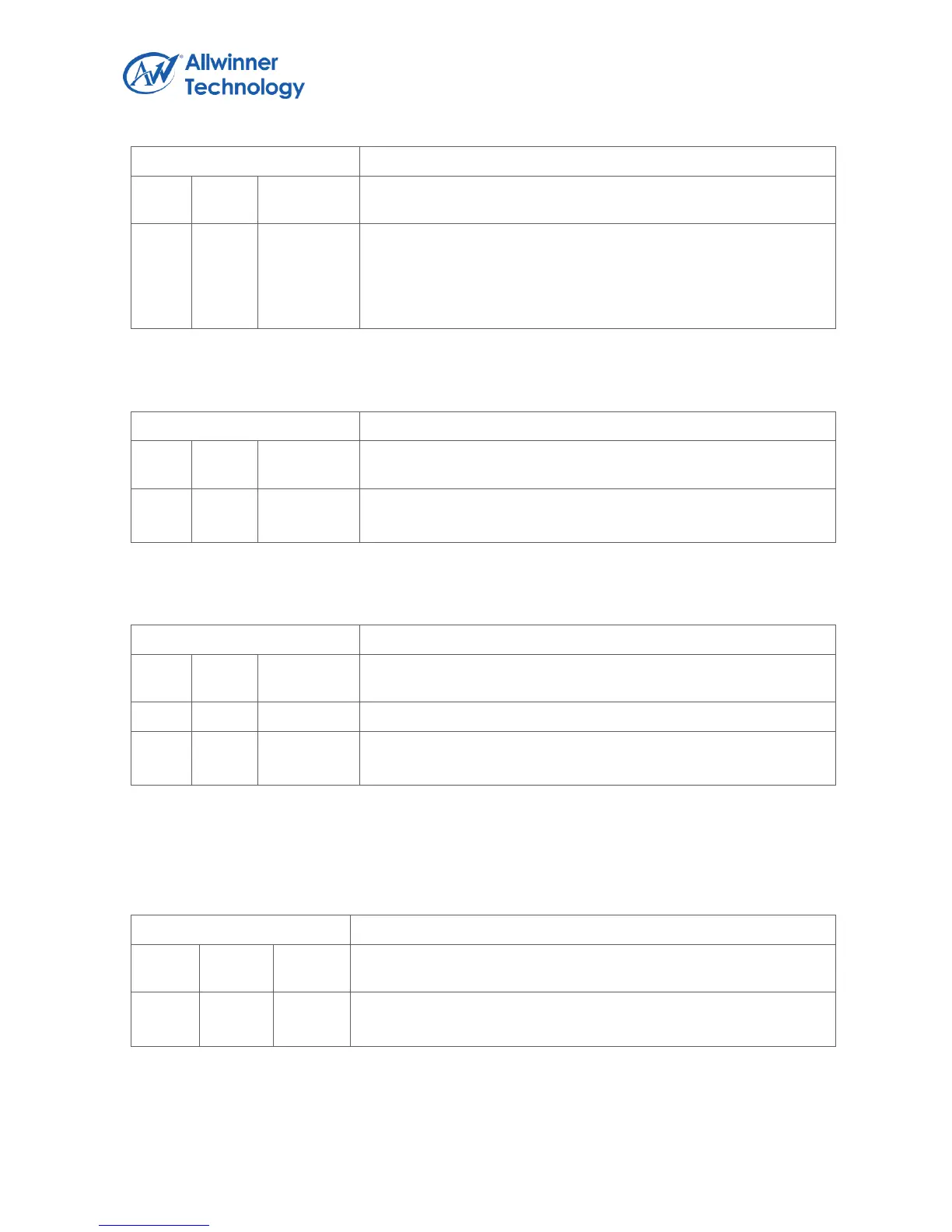

1.10.3.14. HS TIMER 2 INTERVAL VALUE LO REGISTER

Register Name: HS_TMR2_INTV_LO_REG

HS_TMR2_INTV_VALUE_LO.

High Speed Timer 2 Interval Value [31:0].

1.10.3.15. HS TIMER 2 INTERVAL VALUE HI REGISTER

Register Name: HS_TMR2_INTV_HI_REG

HS_TMR2_INTV_VALUE_HI.

High Speed Timer 2 Interval Value [55:32].

Note: the interval value register is a 56-bit register. When read or write the interval value, the Lo

register should be read or written first. And the Hi register should be written after the Lo register.

1.10.3.16. HS TIMER 2 CURRENT VALUE LO REGISTER

Register Name: HS_TMR2_CURNT_LO_REG

HS_TMR2_CUR_VALUE_LO.

High Speed Timer 2 Current Value [31:0].

Loading...

Loading...