A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 161 / 812

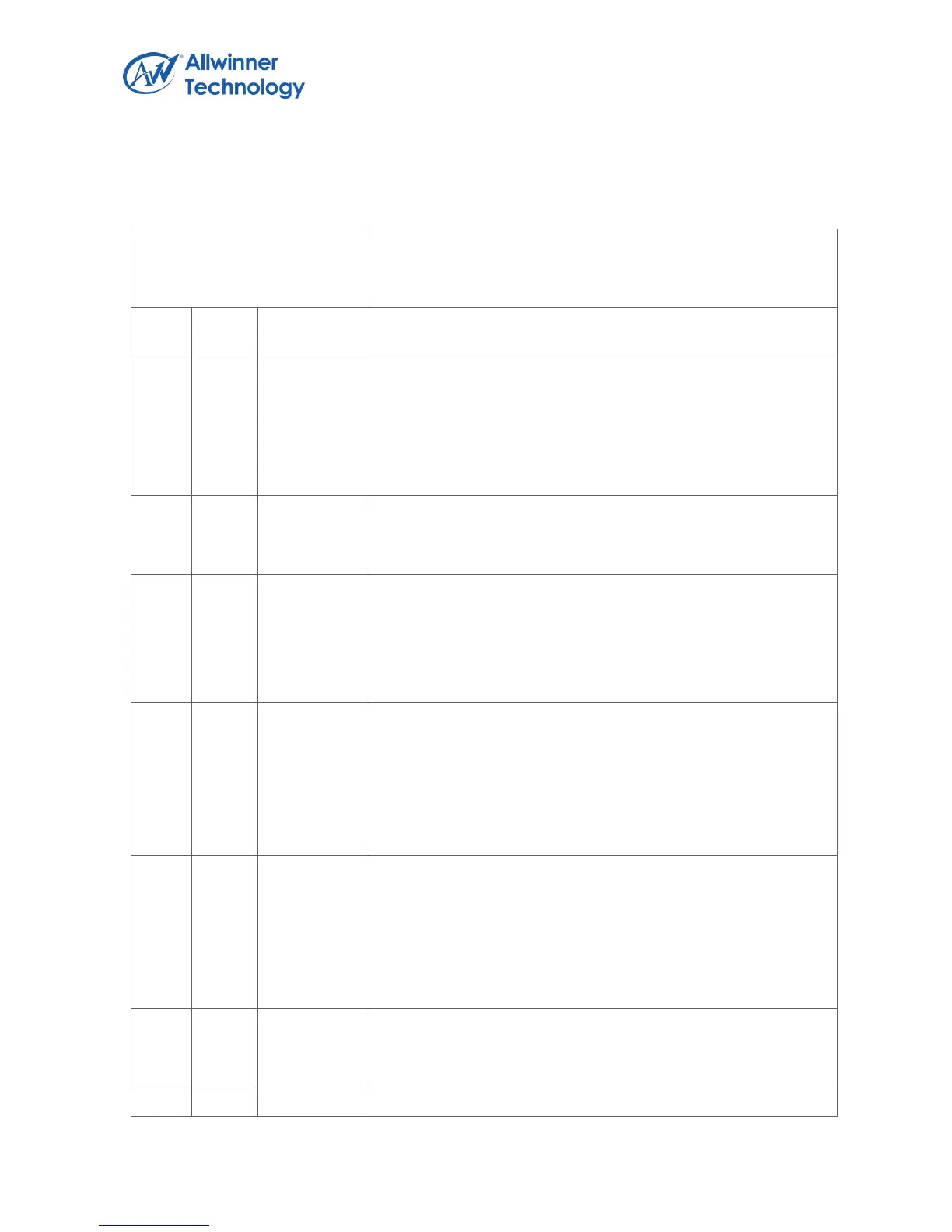

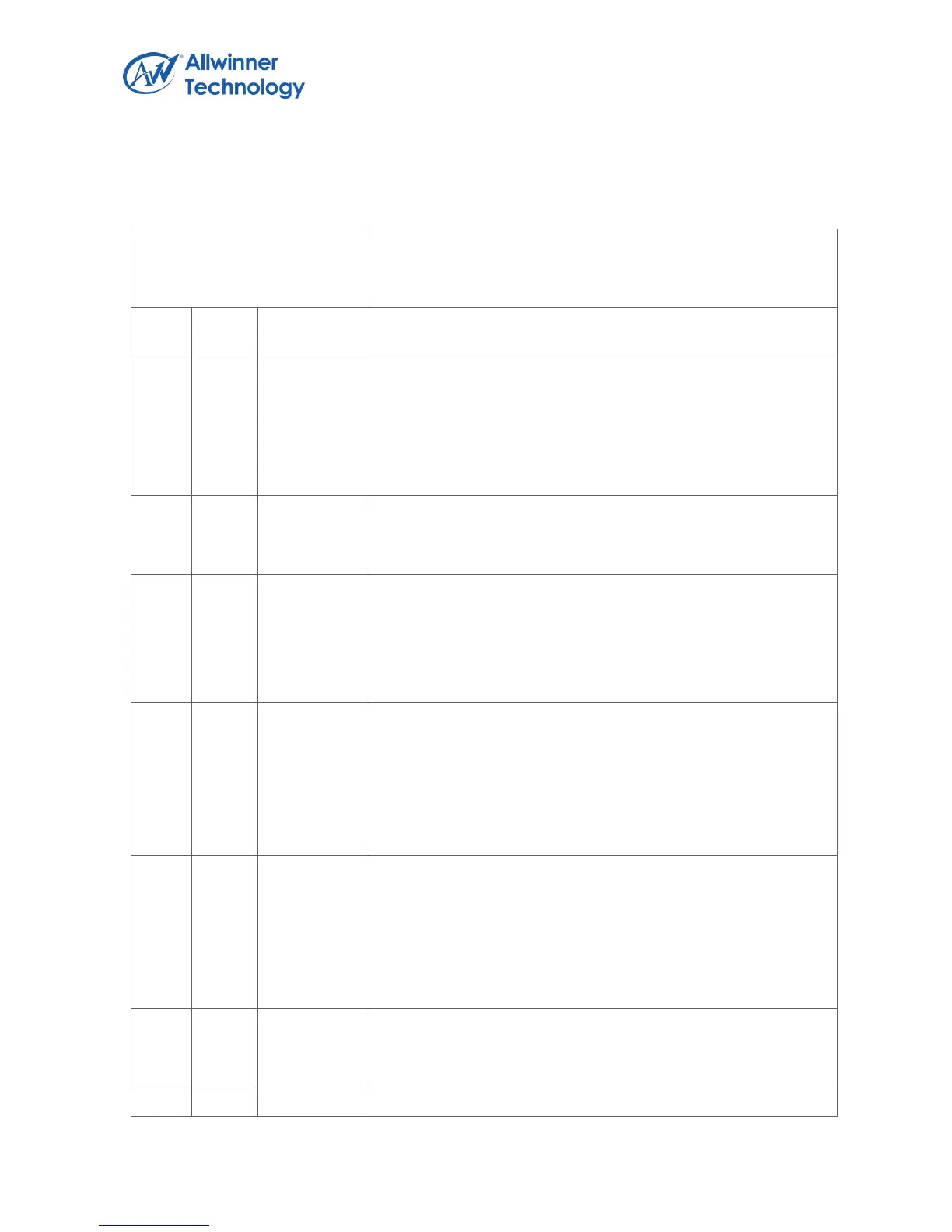

1.12.3.4. NORMAL DMA CONFIGURATION REGISTER(DEFAULT: 0X00000000)

Offset:

0x100+N*0x20

(N=0,1,2,3,4,5,6,7)

Register Name: NDMA_CTRL_REG

DMA_LOADING.

DMA Loading.

If set to 1, DMA will start and load the DMA registers to the

shadow registers. The bit will hold on until the DMA finished. It

will be cleared automatically.

Set 0 to the bit will reset the corresponding DMA channel.

DMA_CONTI_MODE_EN.

DMA Continuous Mode Enable.

0: Disable, 1: Enable.

DMA_WAIT_STATE.

DMA Wait State.

0: wait for 0 DMA clock to request,

…

7: wait for 2

(n+1)

DMA clock to request.

NDMA_DEST_DATA_WIDTH.

Normal DMA Destination Data Width.

00: 8-bit

01: /

10: 32-bit

11: /

DMA_DEST_BST_LEN.

DMA Destination Burst Length.

00: 1

01: /

10: 8

11: /

DMA_DEST_SEC.

DMA Destination Security

0: secure, 1: non-secure.

Loading...

Loading...