A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 160 / 812

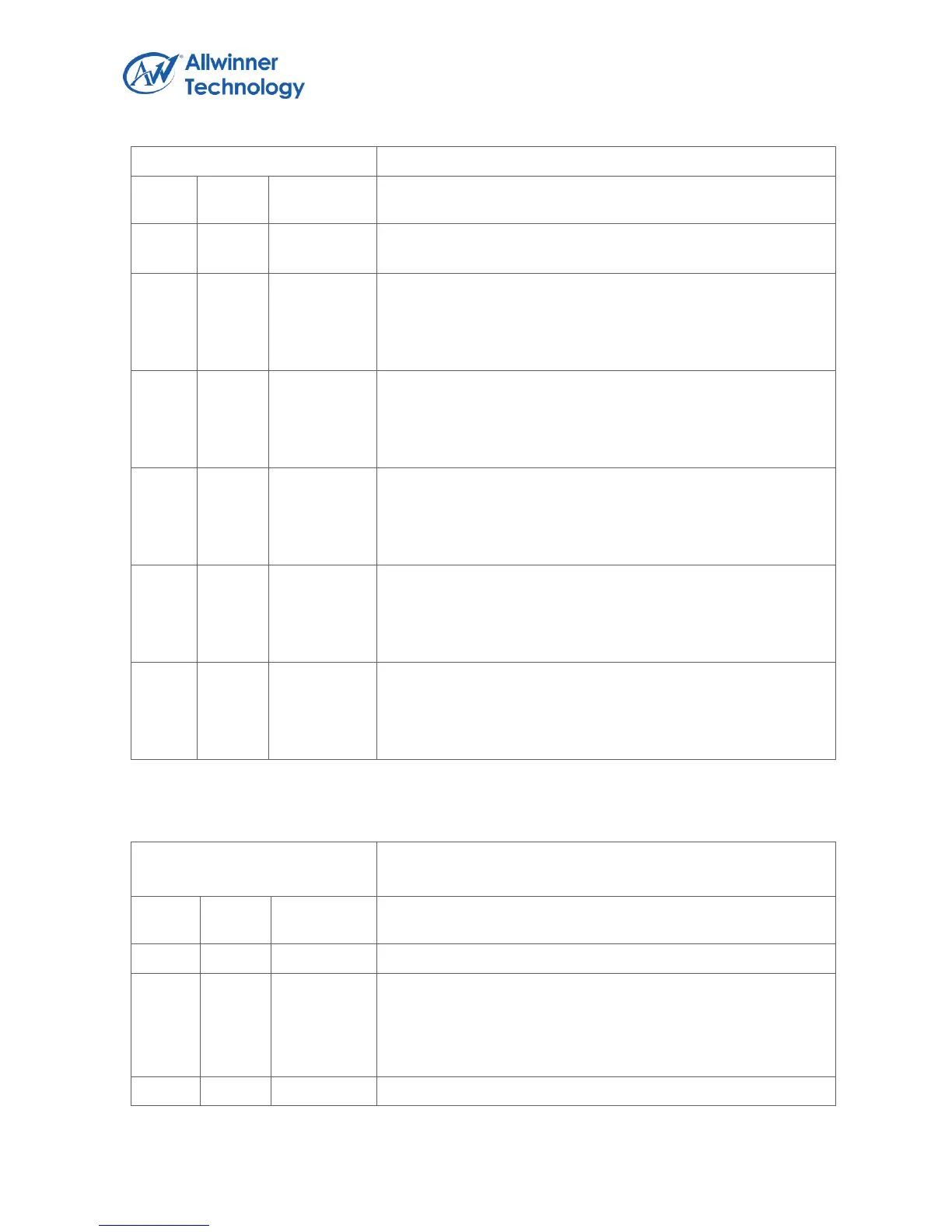

Register Name: DMA_IRQ_PEND_STA_REG

will clear it.

0: No effect, 1: Pending.

NDMA2_HF_IRQ_PEND.

Normal DMA 2 Half Transfer Interrupt Pending. Set 1 to the bit

will clear it.

0: No effect, 1: Pending.

NDMA1_END_IRQ_PEND.

Normal DMA 1 End Transfer Interrupt Pending. Set 1 to the bit

will clear it.

0: No effect, 1: Pending.

NDMA1_HF_IRQ_PEND.

Normal DMA 1 Half Transfer Interrupt Pending. Set 1 to the bit

will clear it.

0: No effect, 1: Pending.

NDMA0_END_IRQ_PEND.

Normal DMA 0 End Transfer Interrupt Pending. Set 1 to the bit

will clear it.

0: No effect, 1: Pending.

NDMA0_HF_IRQ_PEND.

Normal DMA 0 Half Transfer Interrupt Pending. Set 1 to the bit

will clear it.

0: No effect, 1: Pending.

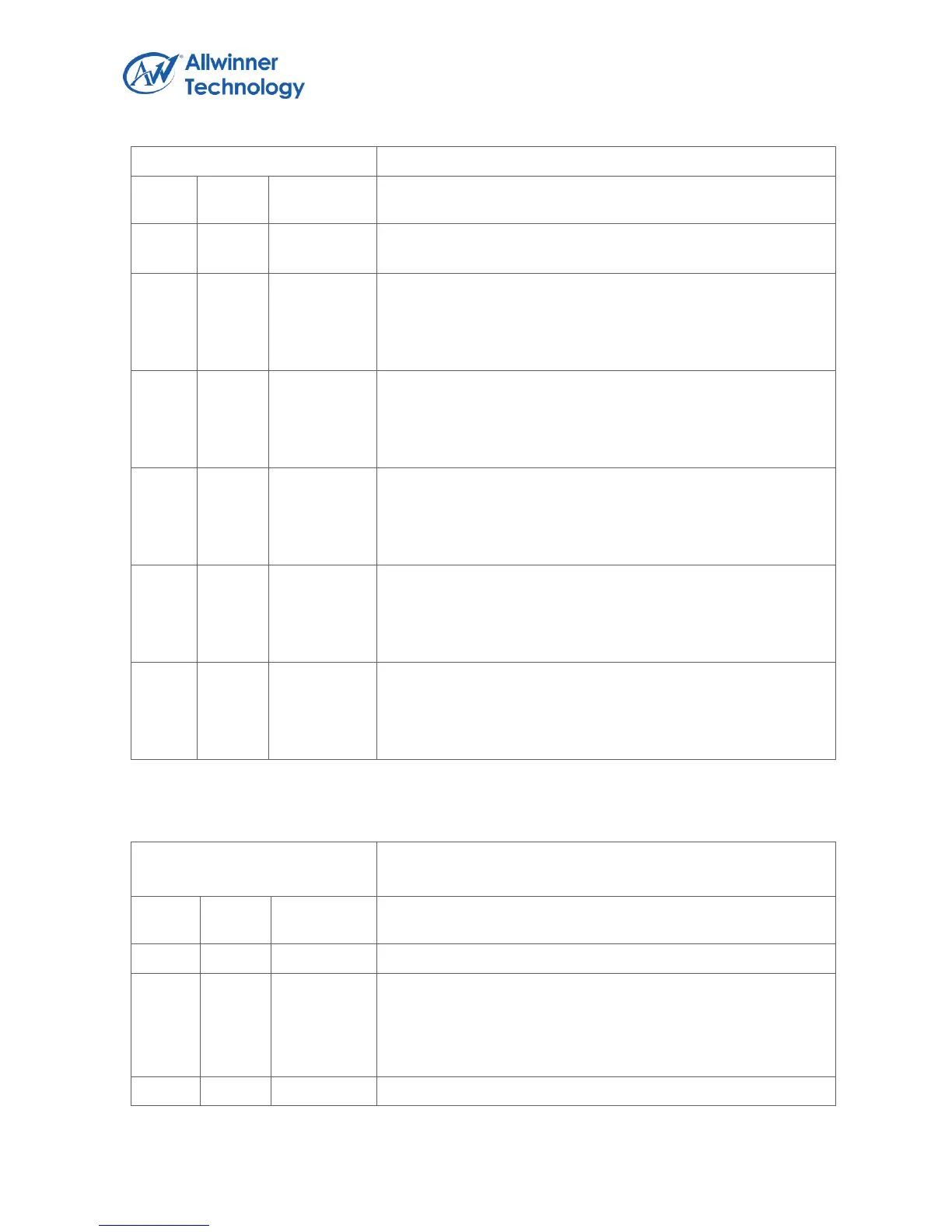

1.12.3.3. NDMA AUTO GATING REGISTER(DEFAULT: 0X00000000)

Register Name: NDMA_AUTO_GAT_REG

Default Value: 0x0000_0000

NDMA Auto Clock Gating bit

0: NDMA auto clock gating enable

1: NDMA auto clock gating disable

If NDMA works in Continuous mode, this bit should be set to 1.

Loading...

Loading...