A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 177 / 812

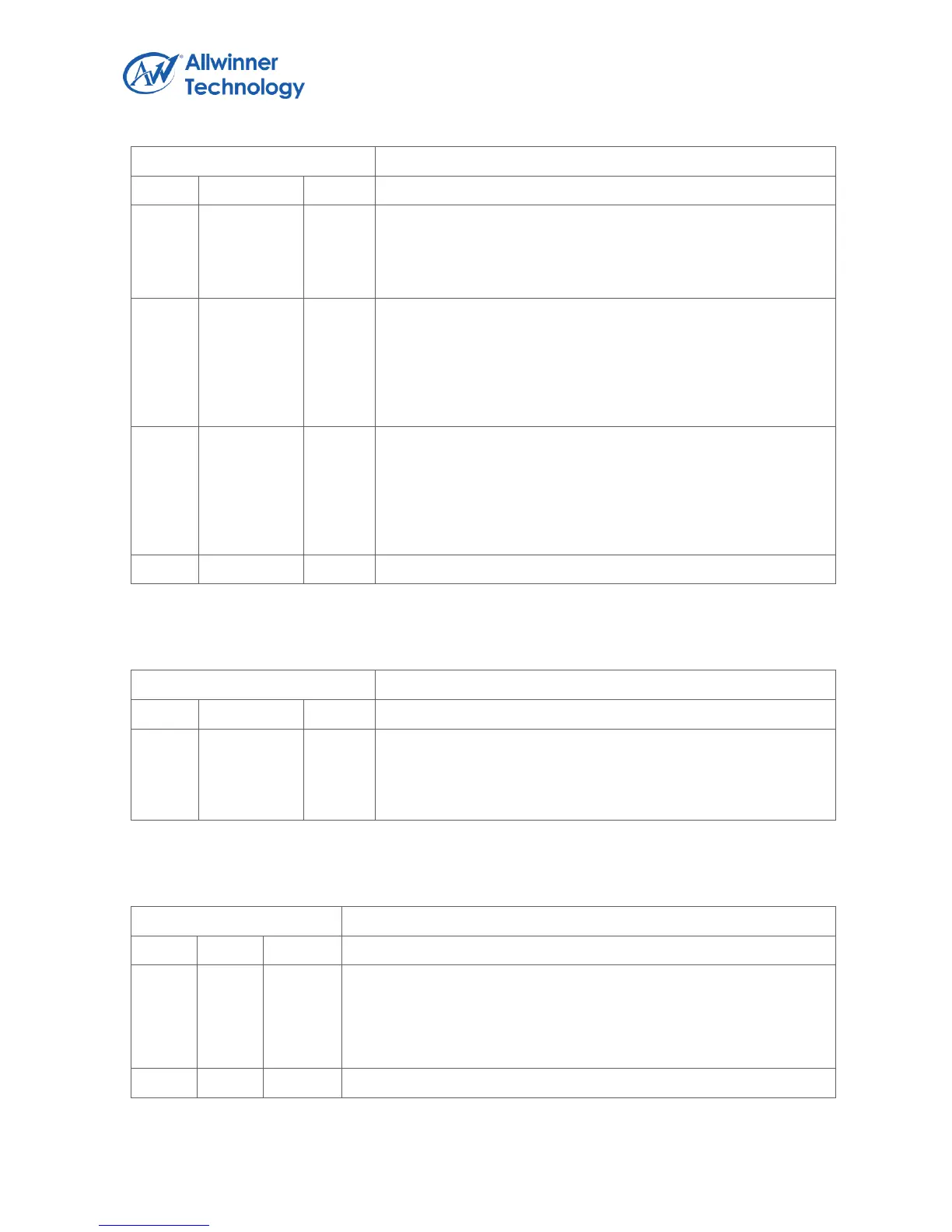

Register Name: AC_DAC_FIFOS

0: No Pending IRQ

1: FIFO Empty Pending Interrupt

Write ‘1’ to clear this interrupt or automatic clear if interrupt

condition fails.

TXU_INT.

TX FIFO Under run Pending Interrupt

0: No Pending Interrupt

1: FIFO Under run Pending Interrupt

Write ‘1’ to clear this interrupt

TXO_INT.

TX FIFO Overrun Pending Interrupt

0: No Pending Interrupt

1: FIFO Overrun Pending Interrupt

Write ‘1’ to clear this interrupt

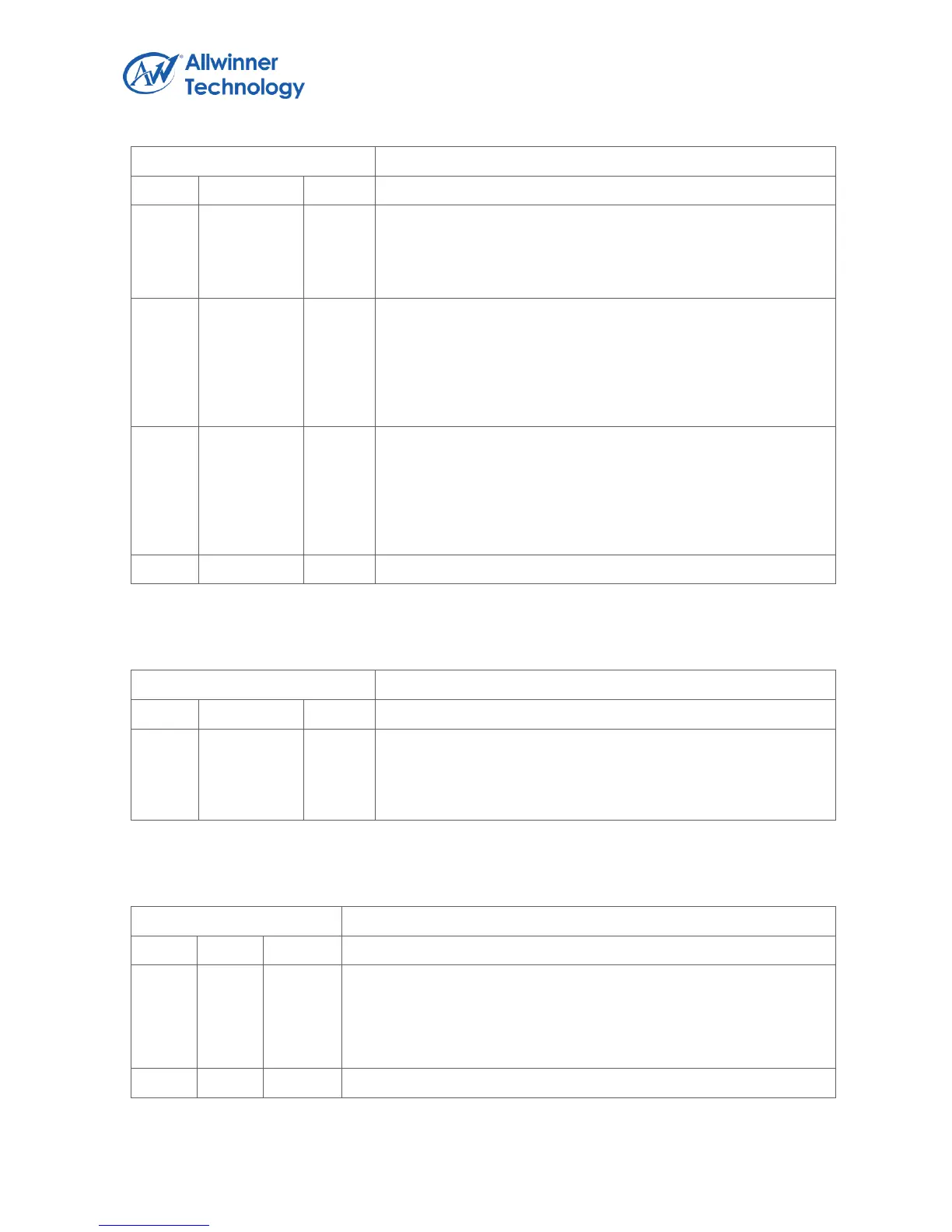

1.13.4.4. DAC TX DATA REGISTER

Register Name: AC_DAC_TXDATA

TX_DATA.

Transmitting left, right channel sample data should be written

this register one by one. The left channel sample data is first

and then the right channel sample.

1.13.4.5. DAC ANALOG CONTROL REGISTER

Register Name: AC_DAC_ACTRL

DACAREN.

Internal DAC Analog Right channel Enable

0:Disable

1:Enable

Loading...

Loading...