A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 195 / 812

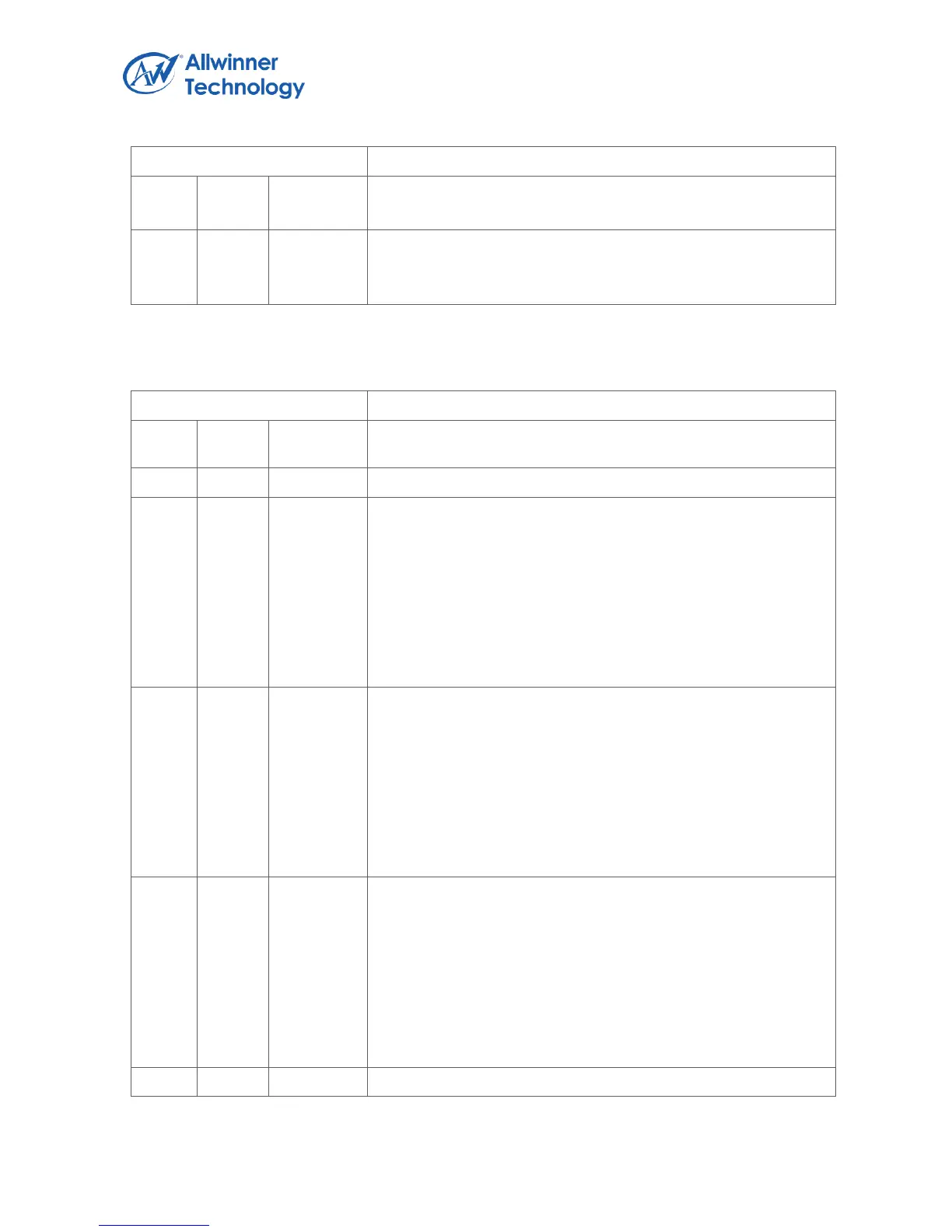

Register Name: LRADC_INTC

ADC 0 Data IRQ Enable

0: Disable

1: Enable

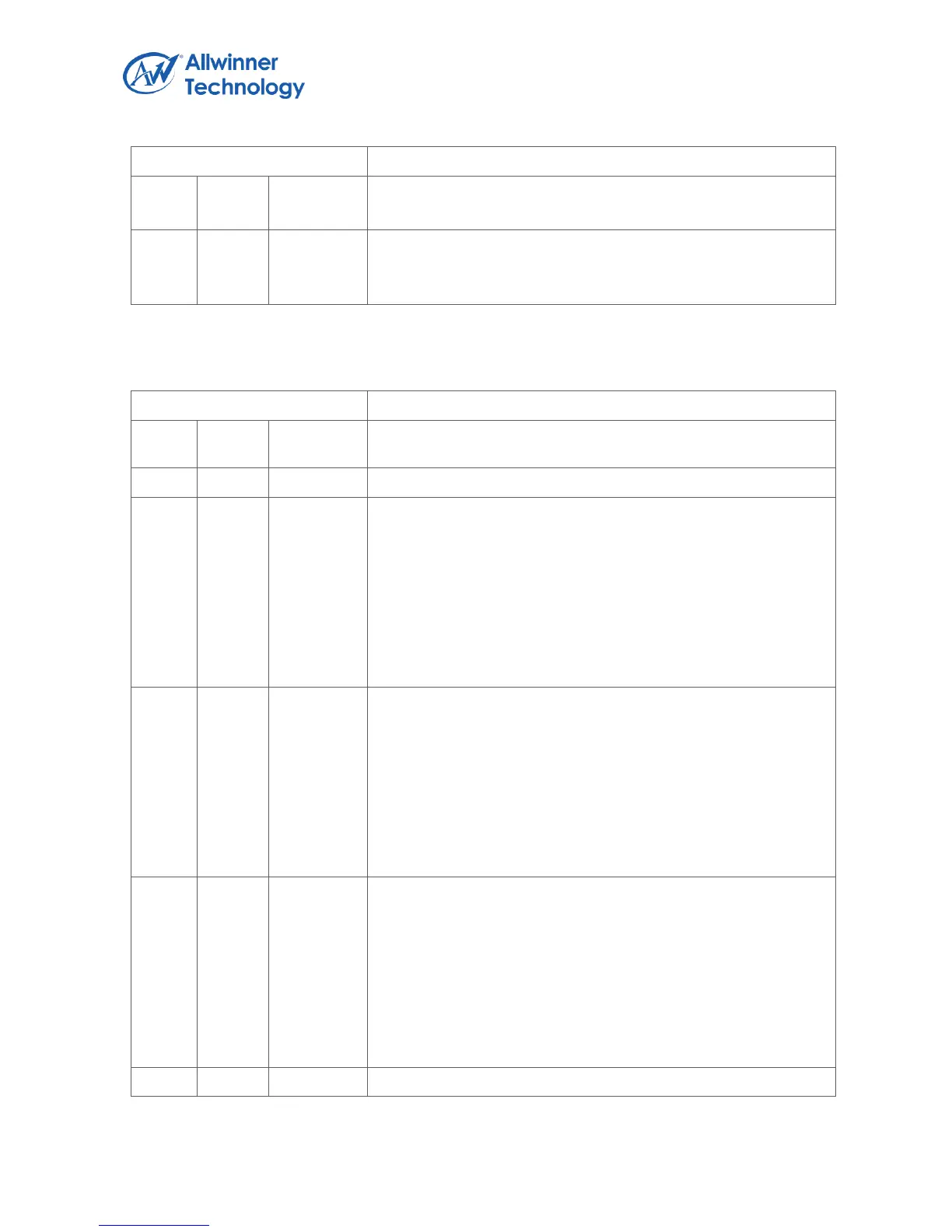

1.14.4.3. LRADC INTERRUPT STATUS REGISTER

ADC1_KEYUP_PENDING.

ADC 1 Key up pending Bit

When general key pull up, it the corresponding interrupt is

enabled.

0: No IRQ

1: IRQ Pending

Notes: Writing 1 to the bit will clear it and its corresponding

interrupt if the interrupt is enable

ADC1_ALRDY_HOLD_PENDING.

ADC 1 Already Hold Pending Bit

When hold key pull down and pull the general key down, if the

corresponding interrupt is enabled.

0: No IRQ

1: IRQ Pending

Notes: Writing 1 to the bit will clear it and its corresponding

interrupt if the interrupt is enable

ADC1_HOLDKEY_PENDING.

ADC 1 Hold Key pending Bit

When Hold key pull down, the status bit is set and the interrupt

line is set if the corresponding interrupt is enabled.

0: NO IRQ

1: IRQ Pending

Notes: Writing 1 to the bit will clear it and its corresponding

interrupt if the interrupt is enable.

ADC1_KEYDOWN_IRQ_PENDING.

Loading...

Loading...