A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 223 / 812

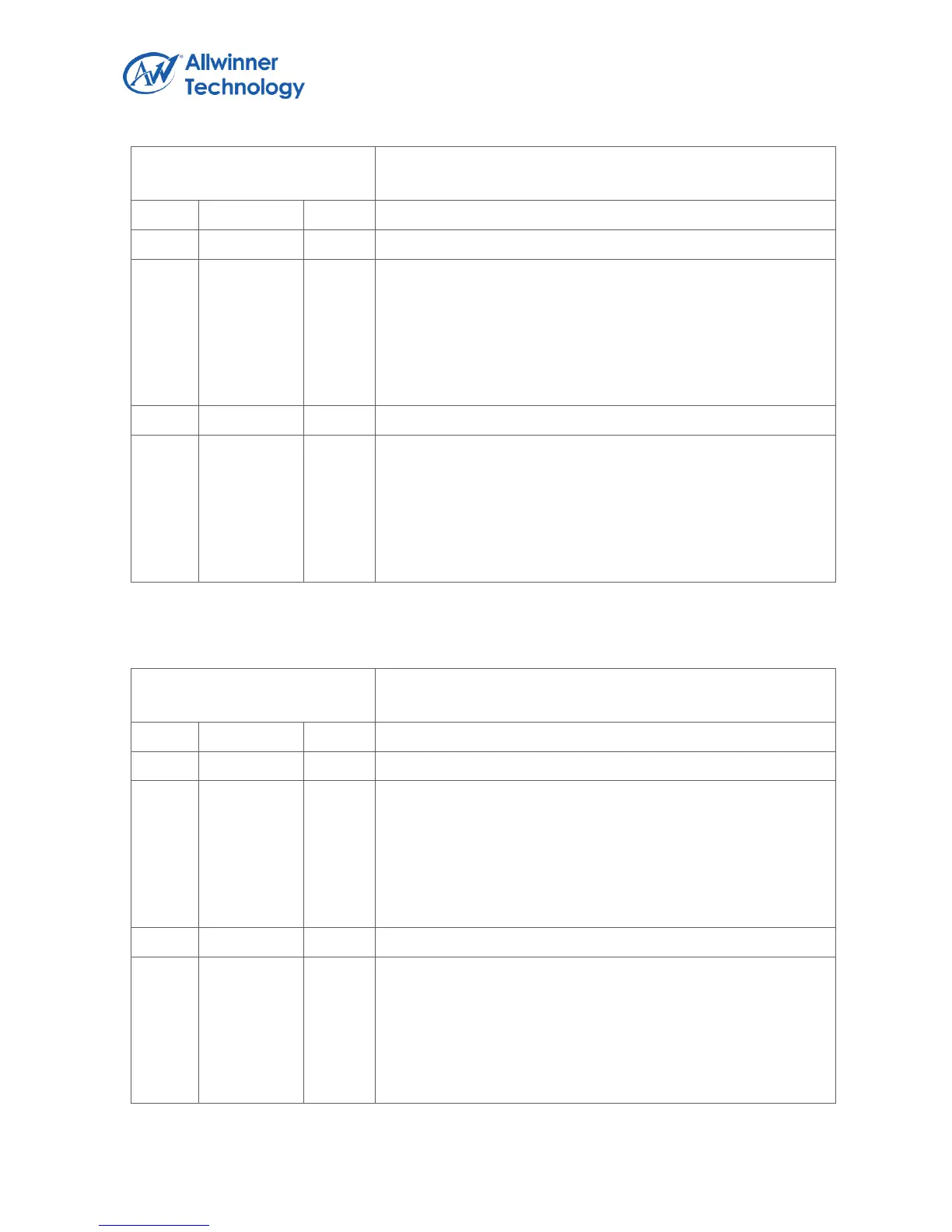

Register Name: SS_FCSR

Default Value: 0x6000_0F0F

RXFIFO_INT_TRIG_LEVEL

RX FIFO Empty Trigger Level

Interrupt and DMA request trigger level for RXFIFO normal

condition

Trigger Level = RXTL + 1

Notes: RX FIFO is used for input the data.

TXFIFO_INT_TRIG_LEVEL

TX FIFO Trigger Level

Interrupt and DMA request trigger level for TXFIFO normal

condition

Trigger Level = TXTL + 1

Notes: TX FIFO is used for output the result data.

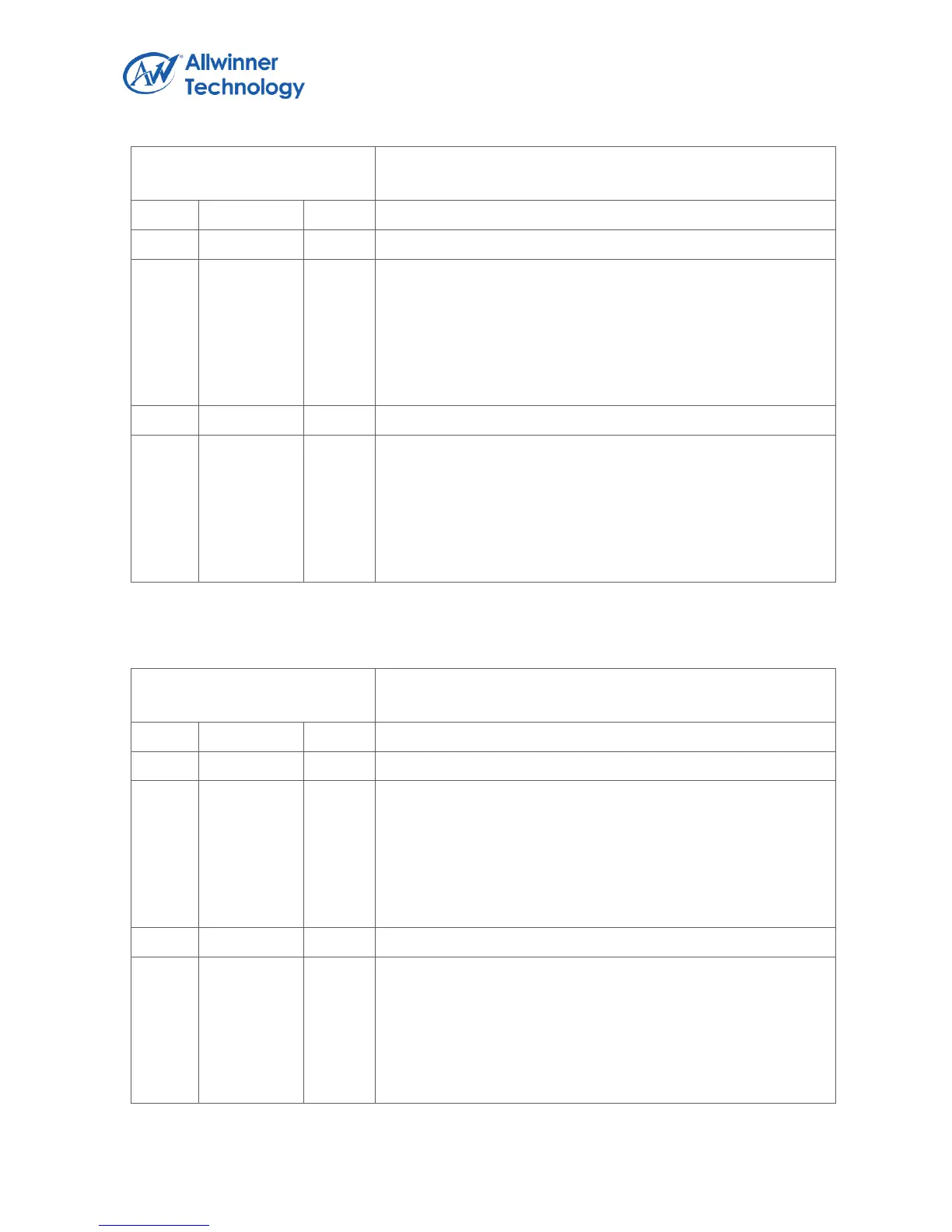

1.16.4.6. SECURITY SYSTEM INTERRUPT CONTROL/ STATUS REGISTER

Register Name: SS_ICSR

Default Value: 0x0000_0000

RXFIFO_EMP_PENDING_BIT

RX FIFO Empty Pending bit

0: No pending

1: RX FIFO Empty pending

Notes: Write ‘1’ to clear or automatic clear if interrupt condition

fails.

TXFIFO_AVA_PENDING_BIT

TX FIFO Data Available Pending bit

0: No TX FIFO pending

1: TX FIFO pending

Notes: Write ‘1’ to clear or automatic clear if interrupt condition

fails.

Loading...

Loading...