A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 285 / 812

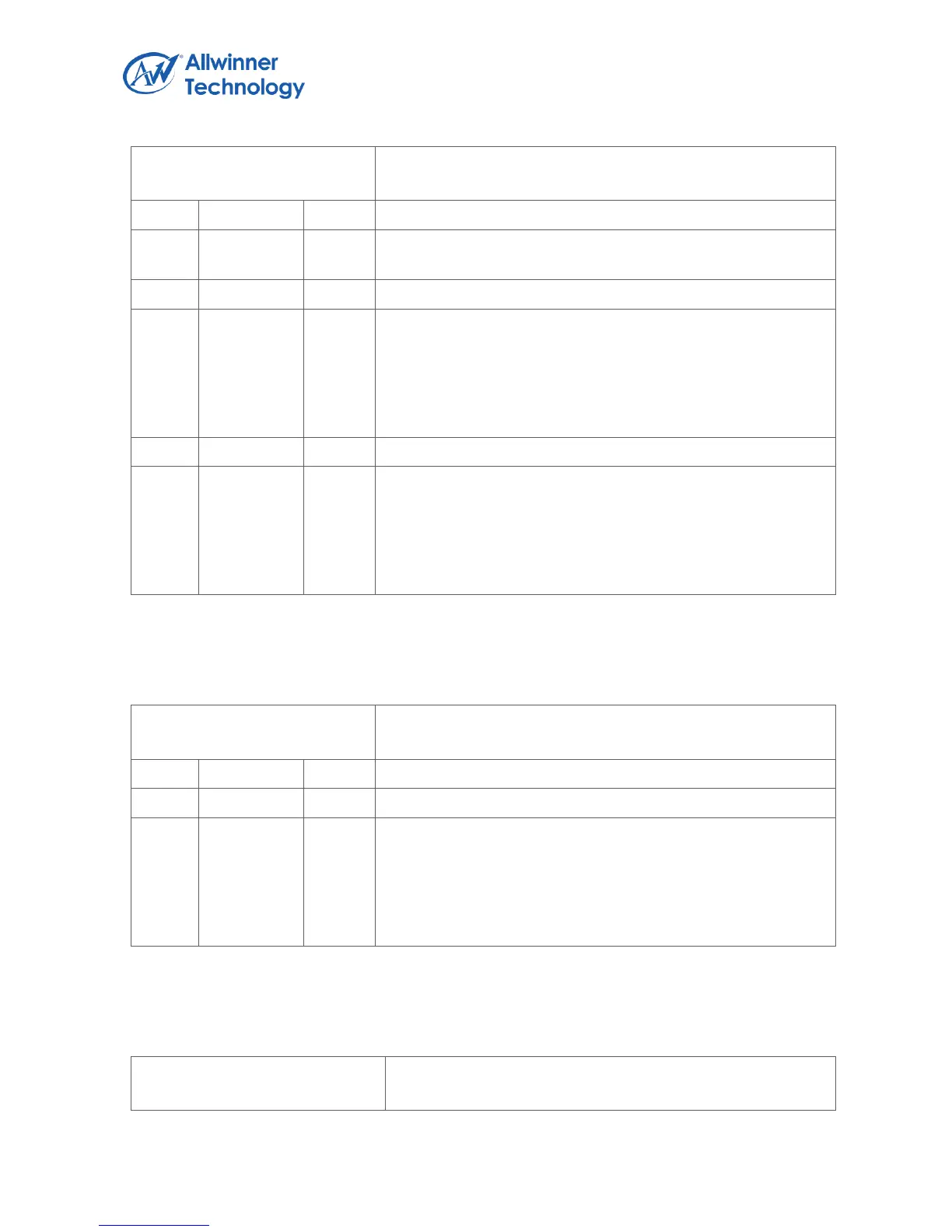

Register Name: PH_CFG3

Default Value: 0x0000_0000

100: KP_OUT6 101: SDC1_D2

110: Reserved 111: CSI1_HSYNC

PH25_SELECT

000: Input 001: Output

010: LCD1_DE 011: ECRS

100: KP_OUT5 101: SDC1_D1

110: Reserved 111: CSI1_FIELD

PH24_SELECT

000: Input 001: Output

010: LCD1_CLK 011: ETXCK

100: KP_OUT4 101: SDC1_D0

110: Reserved 111: CSI1_PCLK

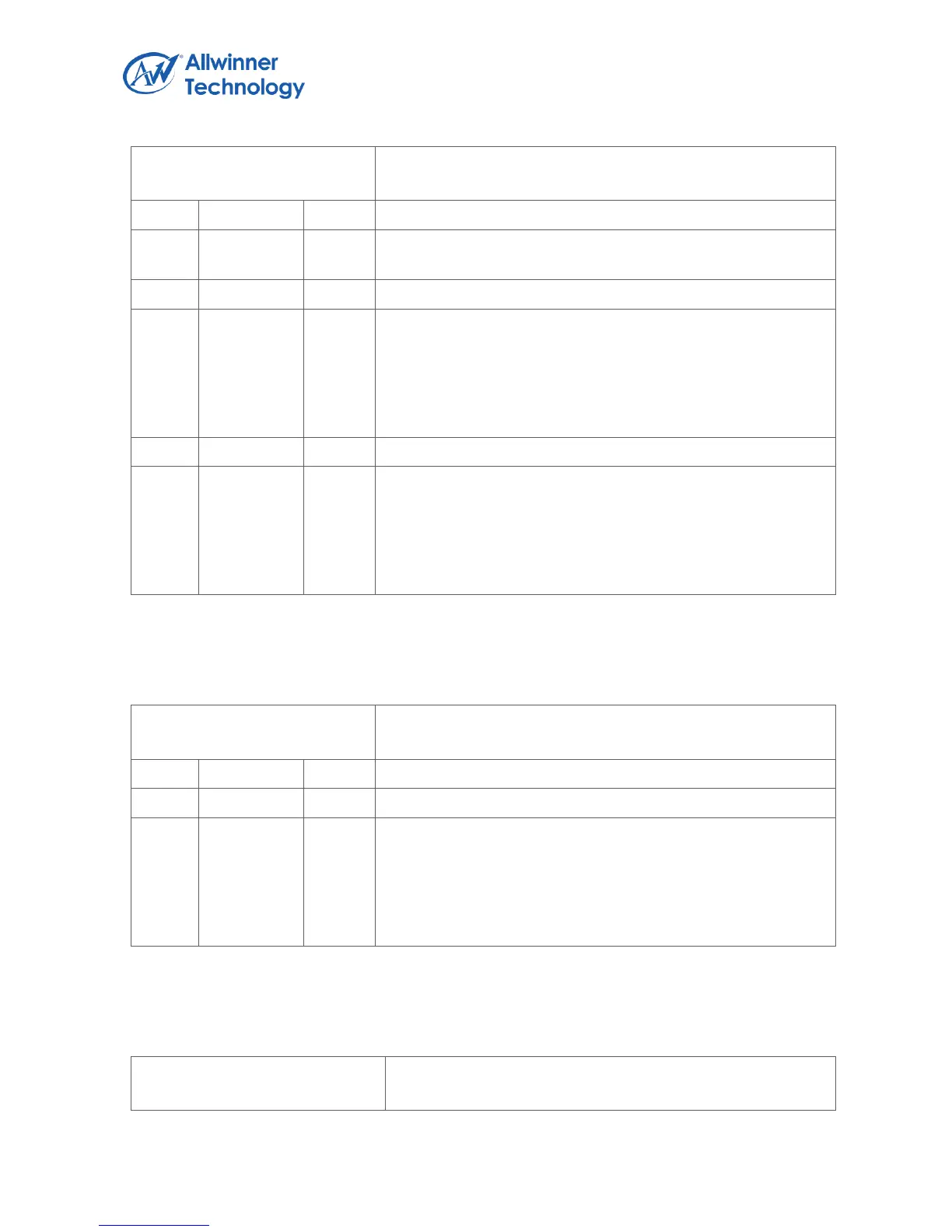

1.19.4.68. PH DATA REGISTER

Register Name: PH_DAT

Default Value: 0x0000_0000

PH_DAT

If the port is configured as input, the corresponding bit is the

pin state. If the port is configured as output, the pin state is the

same as the corresponding bit. The read bit value is the value

setup by software. If the port is configured as functional pin,

the undefined value will be read.

1.19.4.69. PH MULTI-DRIVING REGISTER 0

Register Name: PH_DRV0

Default Value: 0x5555_5555

Loading...

Loading...