A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 367 / 812

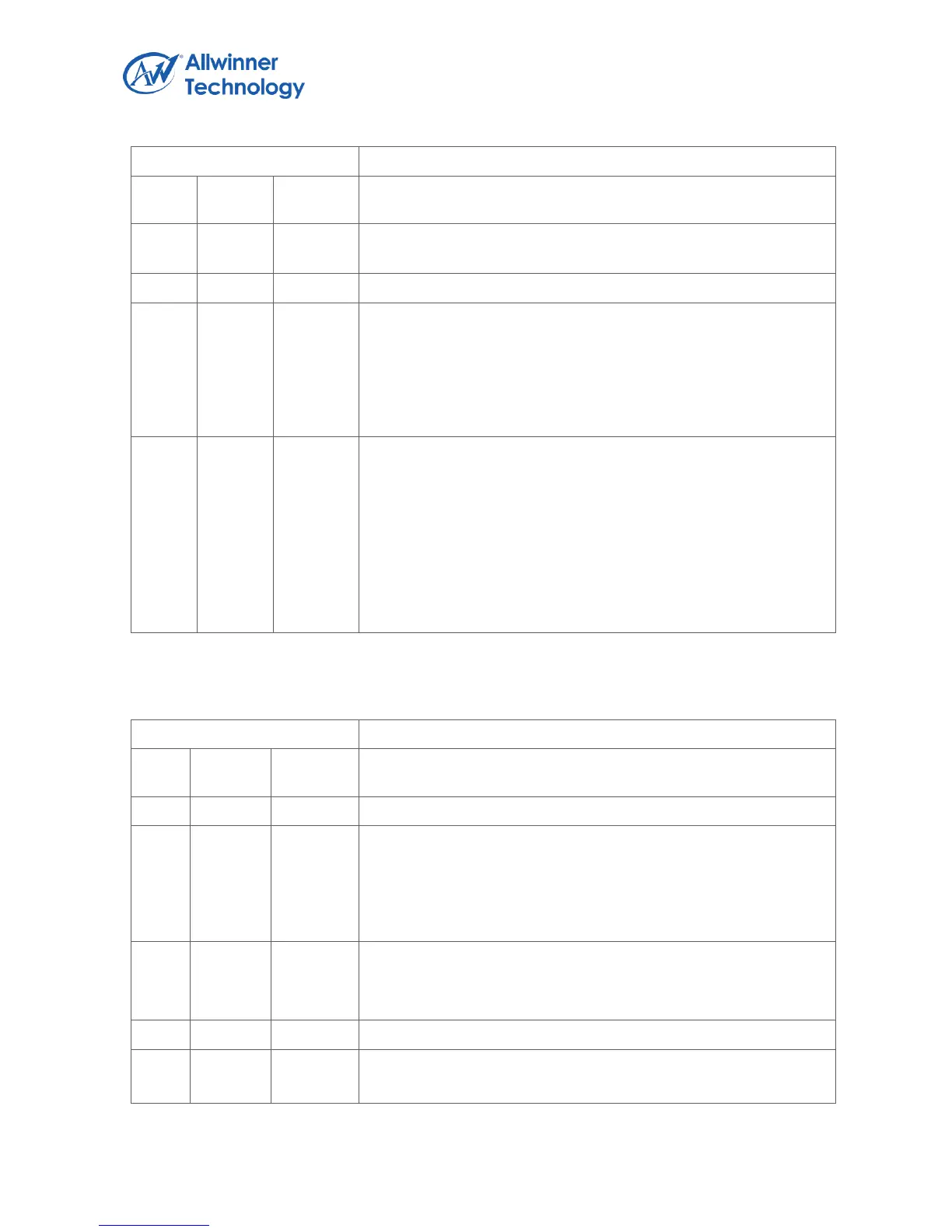

Register Name: CSI0_C0_BUF_STA_REG

For raw data, value = (G>>1+R+G)>>8

For yuv422, value = Y>>8

VCAP_STA

Video capture in progress

Indicates the CSI is capturing video image data (multiple

frames). The bit is set at the start of the first frame after enabling

video capture. When software disables video capture, it clears

itself after the last pixel of the current frame is captured.

SCAP_STA

Still capture in progress

Indicates the CSI is capturing still image data (single frame). The

bit is set at the start of the first frame after enabling still frame

capture. It clears itself after the last pixel of the first frame is

captured.

For CCIR656 interface, if the output format is frame planar

YCbCr 420 mode, the frame end means the field2 end, the other

frame end means filed end.

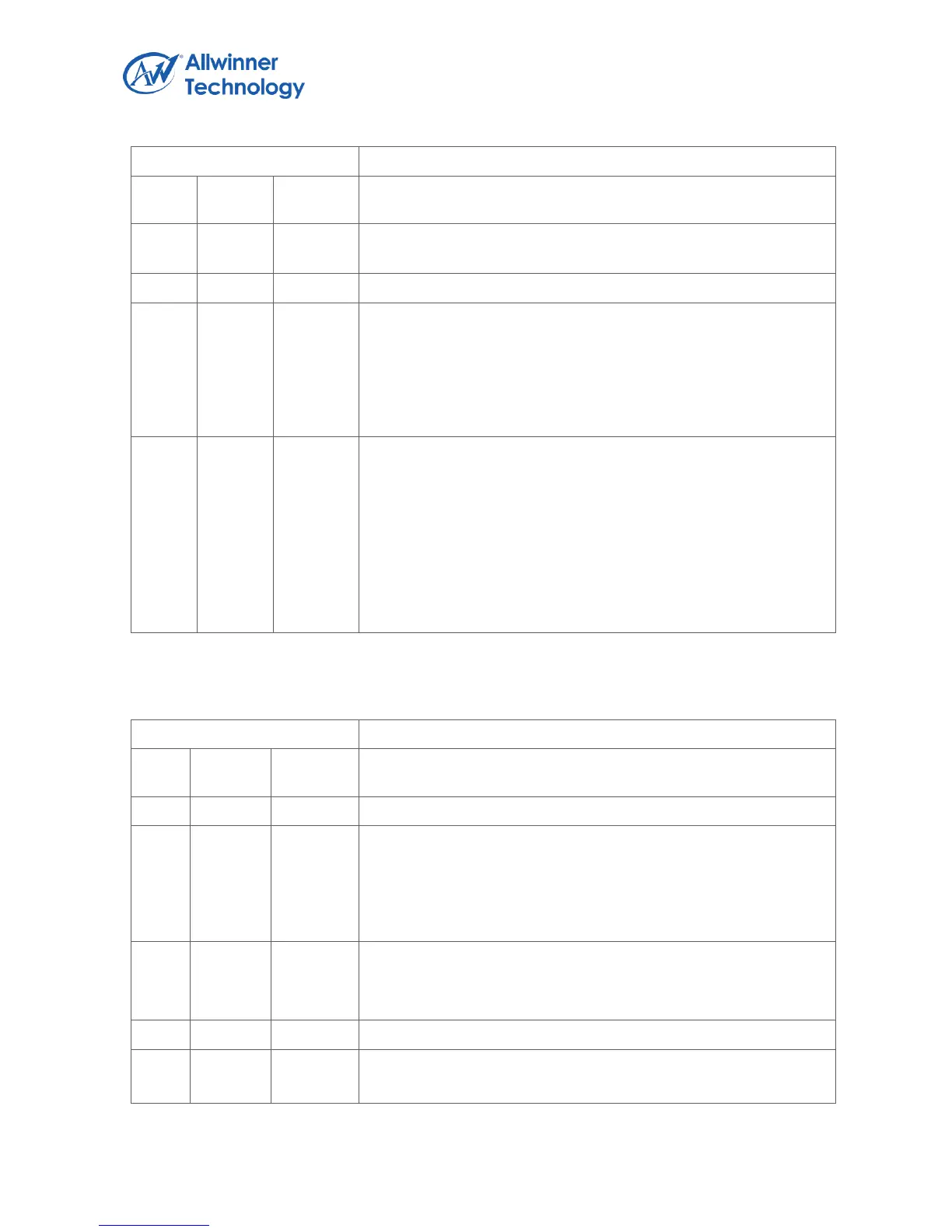

4.1.5.13. CSI CHANNEL_0 INTERRUPT ENABLE REGISTER

Register Name: CSI0_C0_INT_EN_REG

VS_INT_EN

vsync flag

The bit is set when vsync come. And at this time load the buffer

address for the coming frame. So after this irq come, change the

buffer address could only effect next frame

HB_OF_INT_EN

Hblank FIFO overflow

The bit is set when 3 FIFOs still overflow after the hblank.

FIFO2_OF_INT_EN

FIFO 2 overflow

Loading...

Loading...