A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 470 / 812

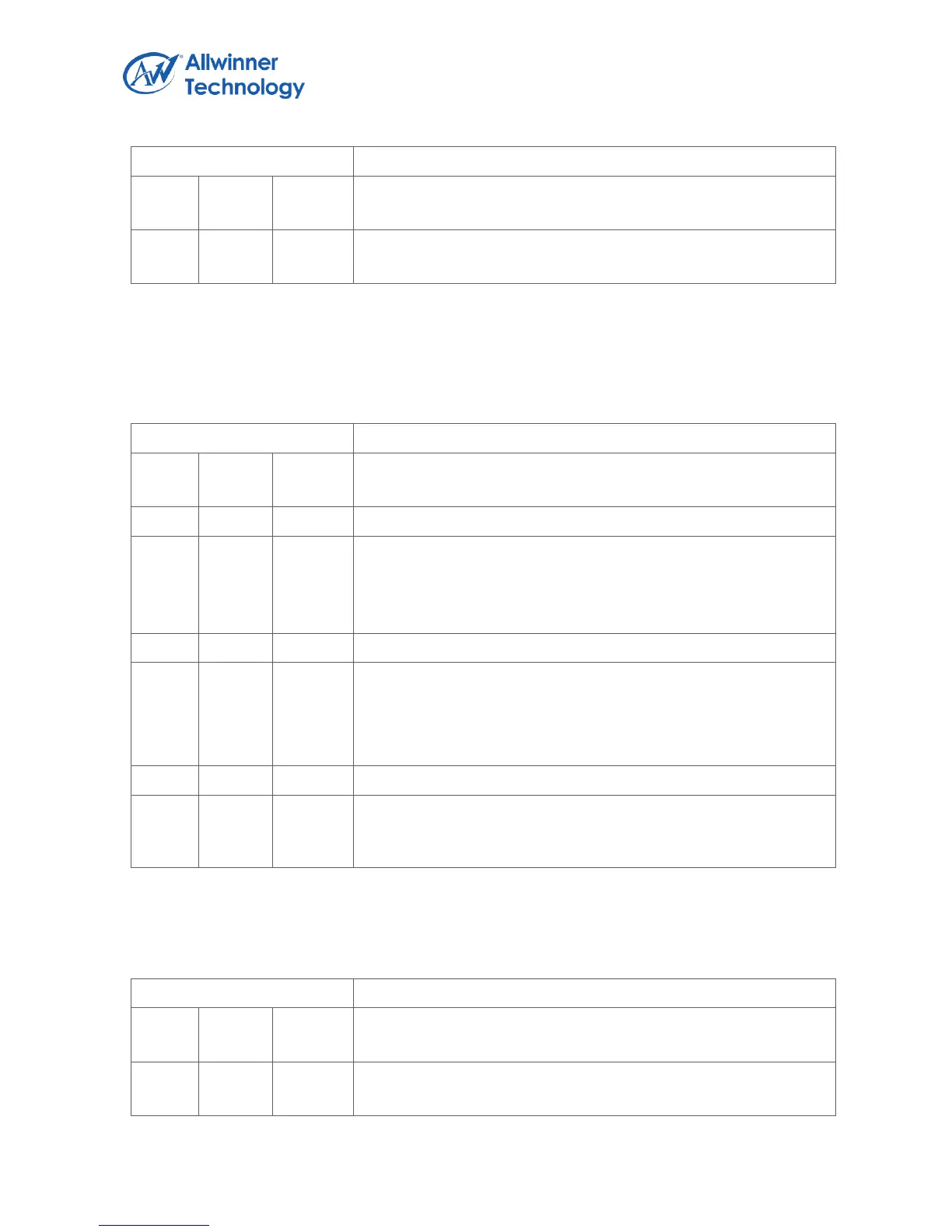

Register name: Aud_TX_FIFO

TX_FIFO

Audio input FIFO port for normal DMA

Note: DMA assume that all sample data are organized as 32-bit/sub-frame.

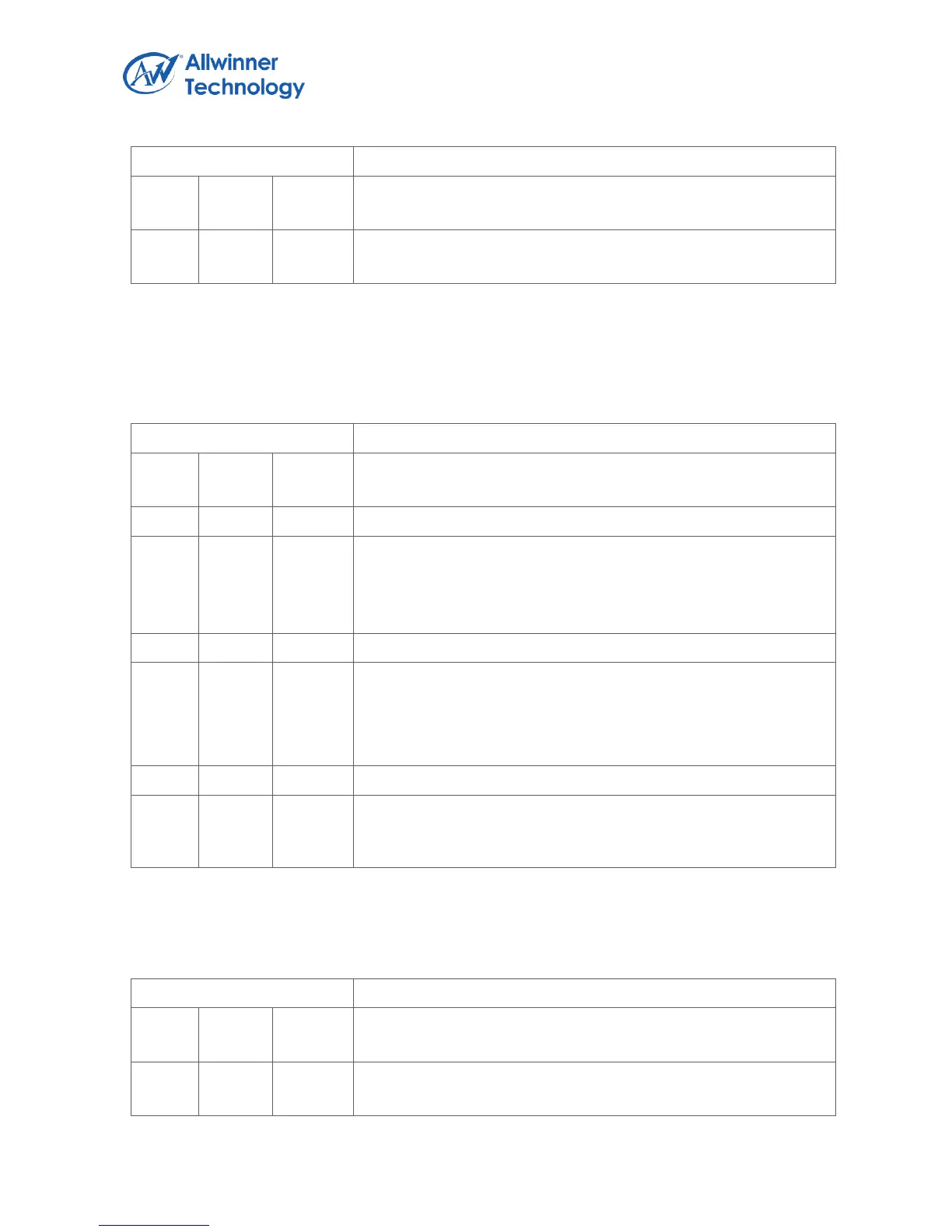

5.2.4.33. DDC CONTROL REGISTER

DDC Access Command Start

Write 1 to this bit will start the DDC Access Command, and will

auto clear when the command complete.

Write ‘0’ to this bit has no effect.

DDC_FIFO_Dir

0: read (HOST<=FIFO<=DEVICE)

1: write (HOST=>FIFO=>DEVICE)

Note: This bit must be set before operation FIFO.

DDC_SW_RST

Write “1” to this bit will clear the DDC controller, and clear to 0

when completing soft reset operation

5.2.4.34. DDC SLAVE ADDRESS REGISTER

Register name: DDC_Slave_Addr

Addr0

Segment pointer for E-DDC read operation

Loading...

Loading...