A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 484 / 812

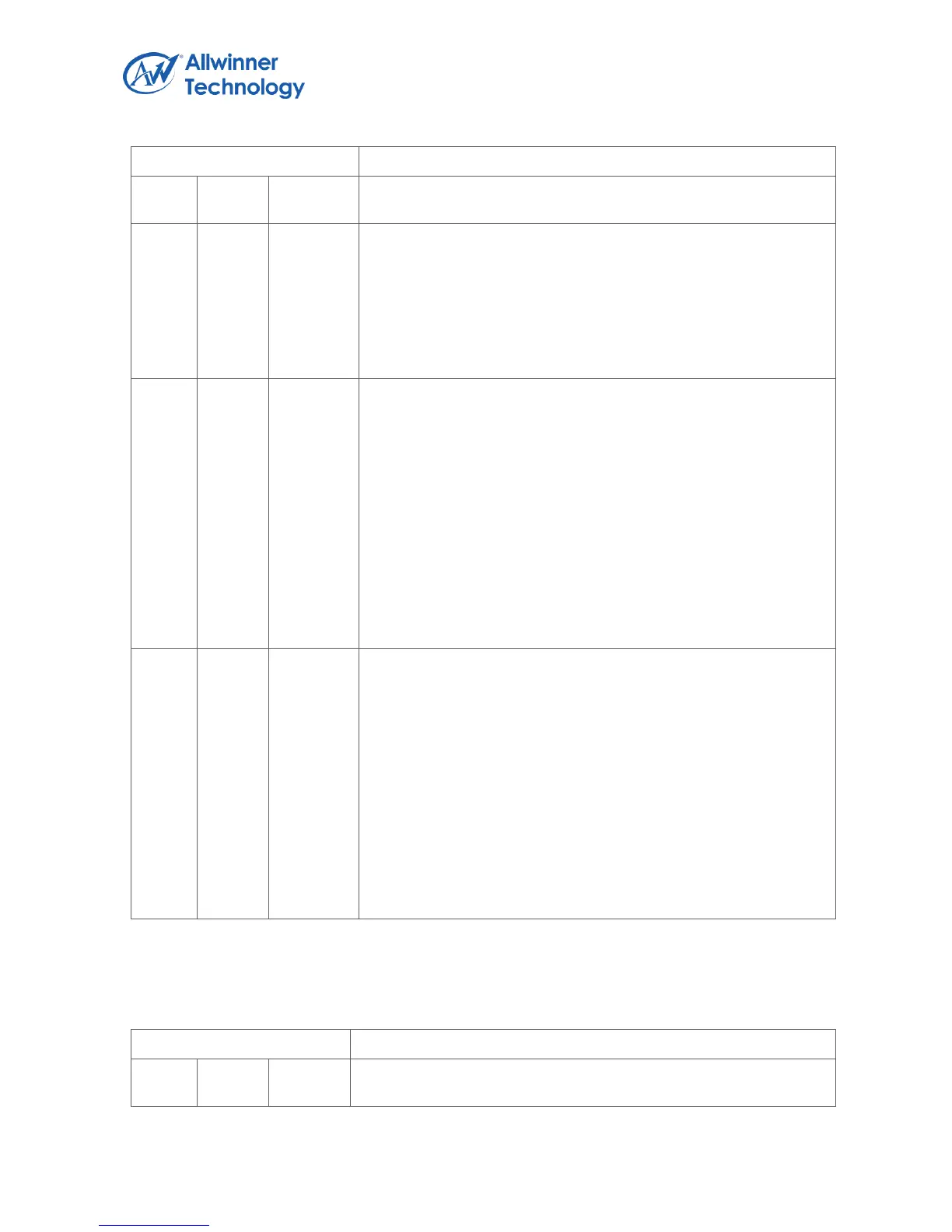

Register Name: DEFE_FRM_CTRL_REG

0: Disable

1: Enable

If output to DEBE is enable, the writing back process will start

when write back enable bit is set and a new frame processing

begins. The bit will be self-cleared when writing-back frame

process starts.

COEF_RDY_EN

Filter coefficients ready enable

0: not ready

1: filter coefficients configuration ready

In order to avoid the noise, you have to ensure the same set filter

coefficients are used in one frame, so the filter coefficients are

buffered, the programmer can change the coefficients in any

time. When the filter coefficients setting is finished, the

programmer should set the bit if the programmer need the new

coefficients in next scaling frame.

When the new frame start, the bit will be self-cleared.

REG_RDY_EN

Register ready enable

0: not ready

1: registers configuration ready

As same as filter coefficients configuration, in order to ensure the

display be correct, the correlative display configuration registers

are buffered too, the programmer also can change the value of

correlative registers in any time. When the registers setting is

finished, the programmer should set the bit if the programmer

need the new configuration in next scaling frame.

When the new frame starts, the bit will also be self-cleared.

Register Name: DEFE_BYPASS_REG

Loading...

Loading...