A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 593 / 812

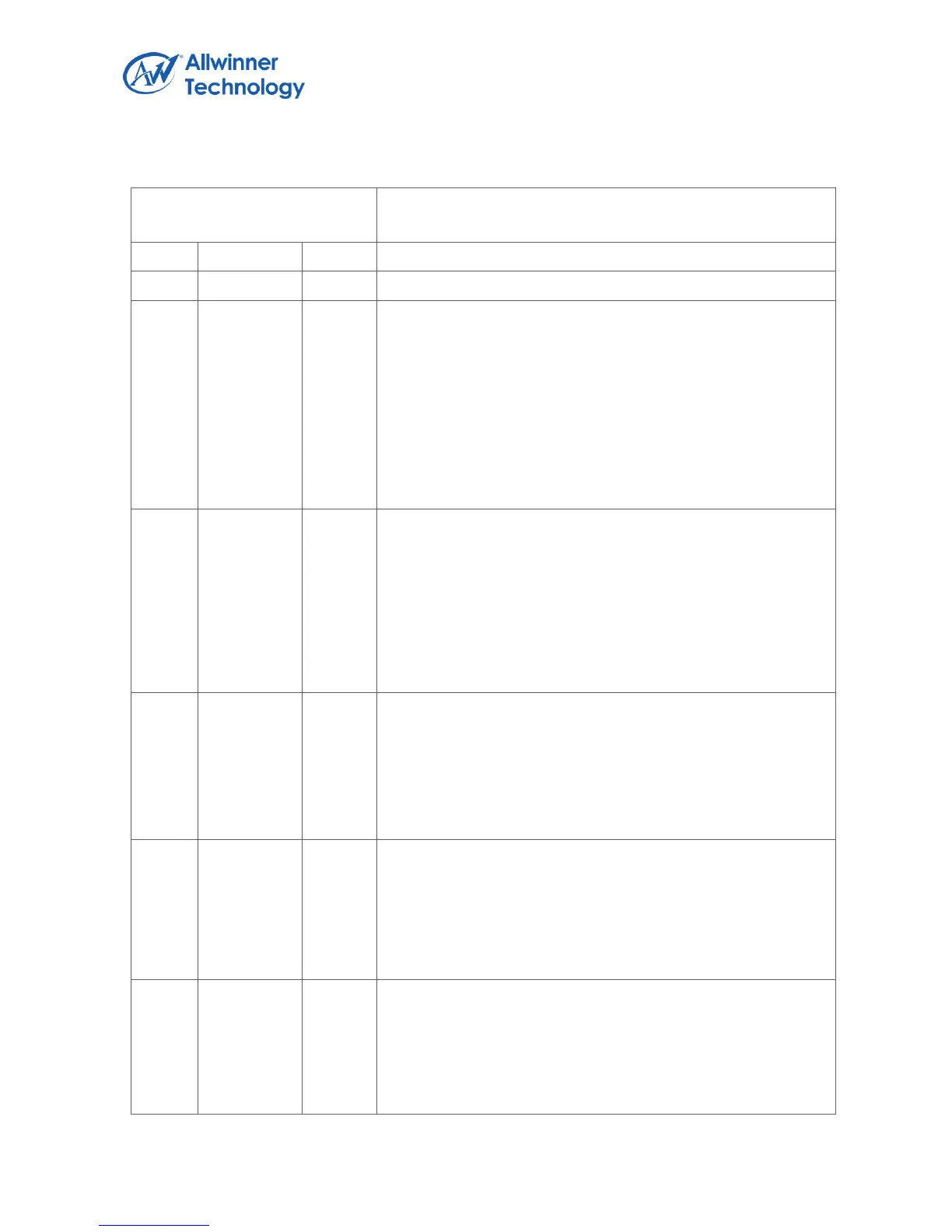

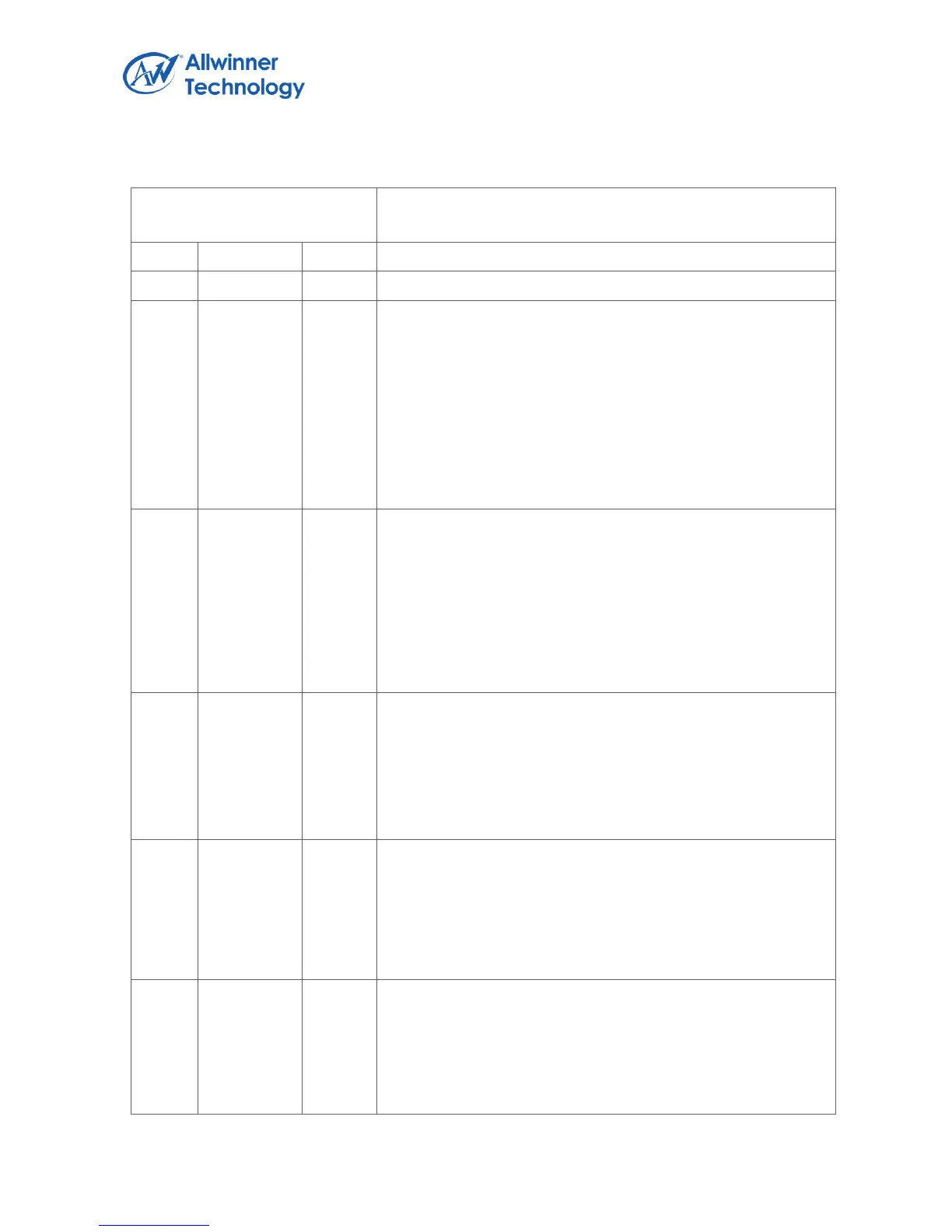

6.3.4.3. SPI CONTROL REGISTER

Register Name: SPI_CTL

Default Value: 0x0012_001C

SDM

Master Sample Data Mode

1 - Normal Sample Mode

0 - Delay Sample Mode

In Normal Sample Mode, SPI master samples the data at the

correct edge for each SPI mode;

In Delay Sample Mode, SPI master samples data at the edge

that is half cycle delayed by the correct edge defined in

respective SPI mode.

SDC

Master Sample Data Control

Set this bit to ‘1’ to make the internal read sample point with a

delay of half cycle of SPI_CLK. It is used in high speed read

operation to reduce the error caused by the time delay of

SPI_CLK propagating between master and slave.

1 – delay internal read sample point

0 – normal operation, do not delay internal read sample point

TP_EN

Transmit Pause Enable

In master mode, it is used to control transmit state machine to

stop smart burst sending when RX FIFO is full.

1 – stop transmit data when RXFIFO full

0 – normal operation, ignore RXFIFO status

SS_LEVEL

When control SS signal manually

(SPI_CTRL_REG.SS_CTRL==1), set this bit to ‘1’ or ‘0’ to

control the level of SS signal.

1 – set SS to high

0 – set SS to low

SS_CTRL

SS Output Mode Select

Usually, controller sends SS signal automatically with data

together. When this bit is set to 1, software must manually

write SPI_CTRL_REG.SS_LEVEL (bit [17]) to 1 or 0 to control

the level of SS signal.

Loading...

Loading...