A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 594 / 812

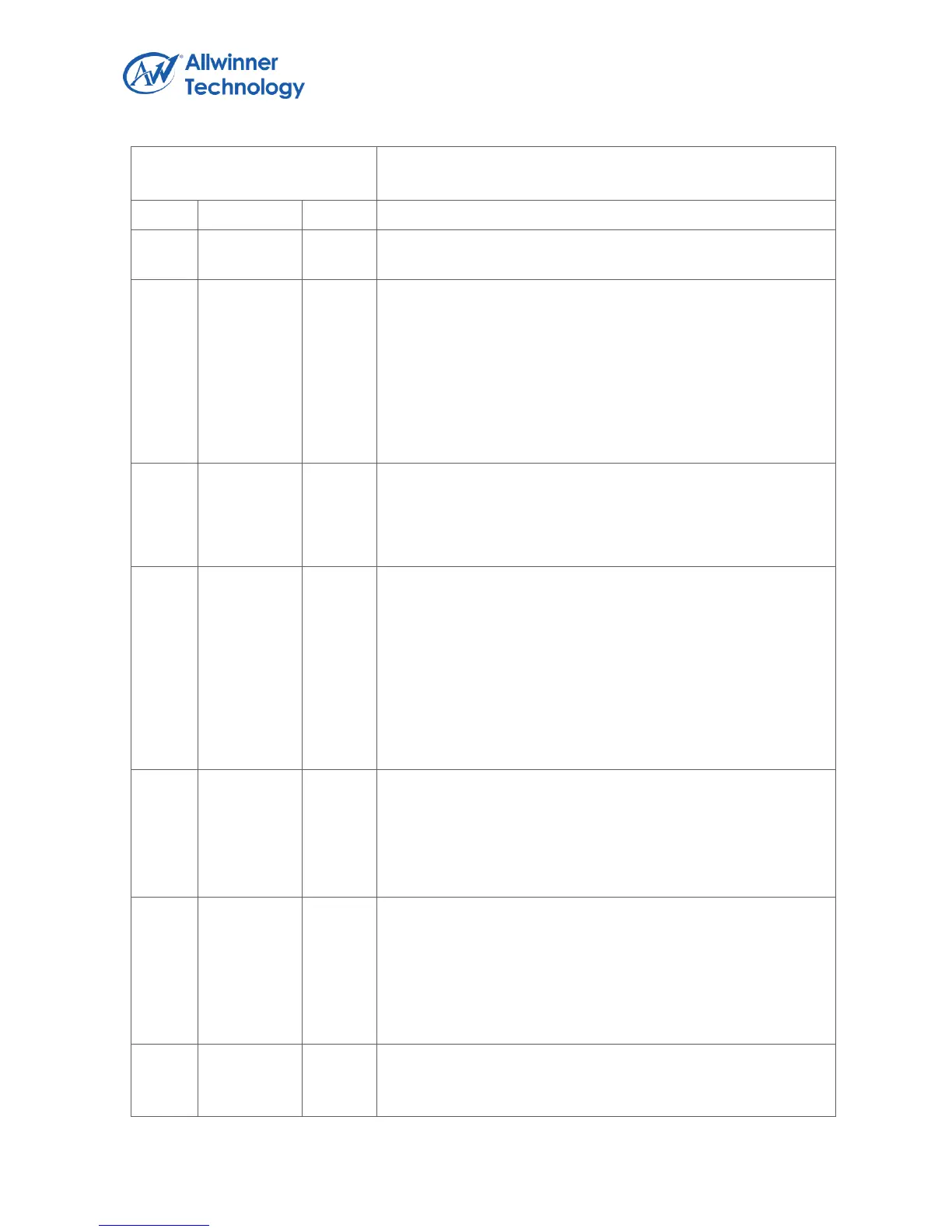

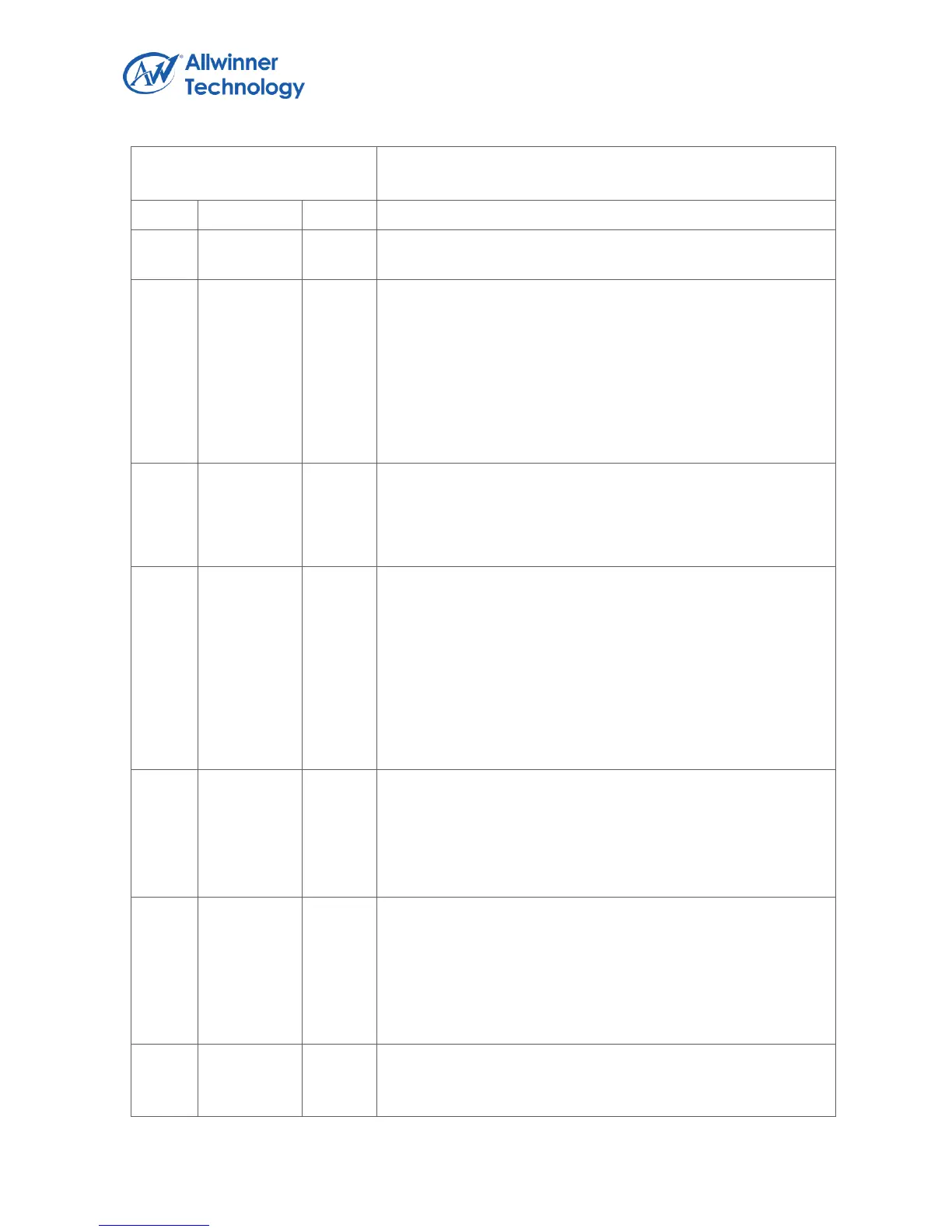

Register Name: SPI_CTL

Default Value: 0x0012_001C

1 – manual output SS

0 – automatic output SS

DHB

Discard Hash Burst

In master mode it controls whether discarding unused SPI

bursts

0: Receiving all SPI bursts in BC period

1: Discard unused SPI bursts, only fetching the SPI bursts

during dummy burst period. The bursts number is specified by

WTC.

DDB

Dummy Burst Type

0: The bit value of dummy SPI burst is zero

1: The bit value of dummy SPI burst is one

SS

SPI Chip Select

Select one of four external SPI Master/Slave Devices

00: SPI_SS0 will be asserted

01: SPI_SS1 will be asserted

10: SPI_SS2 will be asserted

11: SPI_SS3 will be asserted

Notes: This two bits can’t be configured for SPI1 Engine.

RPSM

Rapids mode select

Select rapids operation for high speed read.

0: normal read mode

1: rapids read mode

XCH

Exchange Burst

In master mode it is used to start to SPI burst

0: Idle

1: Initiates exchange. After finishing the SPI bursts transfer

specified by BC, this bit is cleared to zero by SPI Controller.

RF_RST

RXFIFO Reset

Write ‘1’ to reset the control portion of the receiver FIFO and

Loading...

Loading...