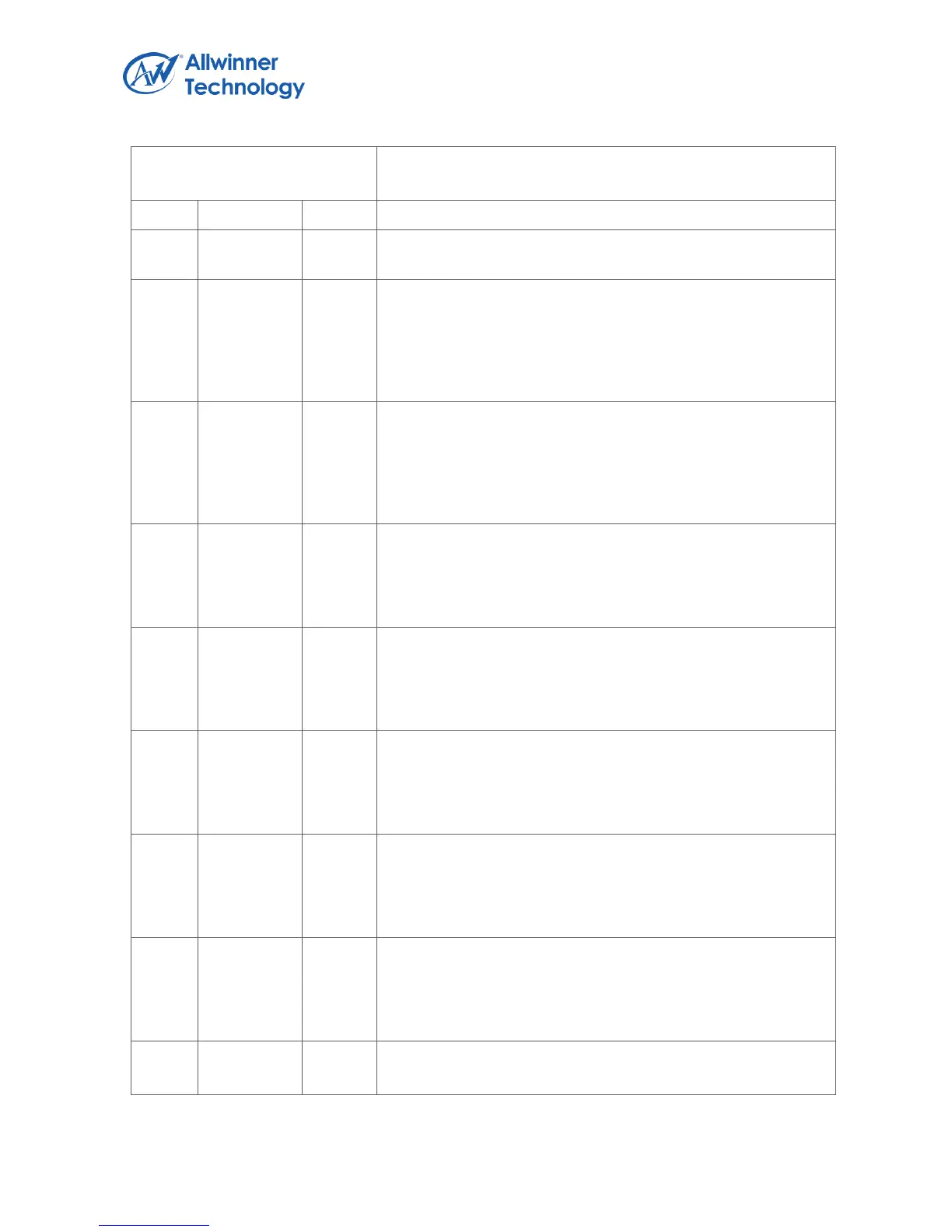

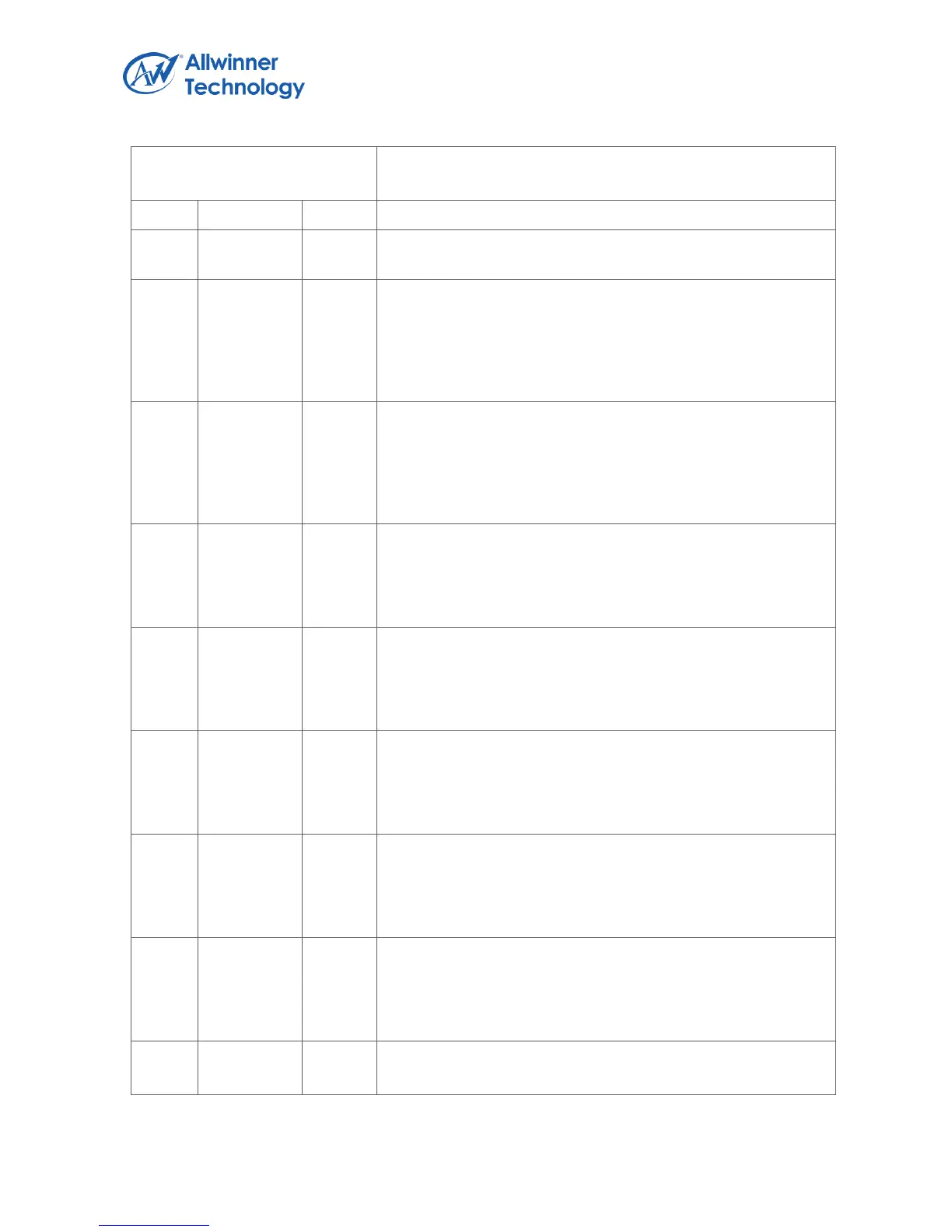

A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 595 / 812

Register Name: SPI_CTL

Default Value: 0x0012_001C

treats the FIFO as empty.

It is 'self-clearing'. It is not necessary to clear this bit.

TF_RST

TXFIFO Reset

Write ‘1’ to reset the control portion of the transmit FIFO and

treats the FIFO as empty.

It is 'self-clearing'. It is not necessary to clear this bit.

SSCTL

In master mode, this bit selects the output wave form for the

SPI_SSx signal.

0: SPI_SSx remains asserted between SPI bursts

1: Negate SPI_SSx between SPI bursts

LMTF

LSB/ MSB Transfer First select

0: MSB first

1: LSB first

DMAMC

SPI DMA Mode Control

0: Normal DMA mode

1: Dedicate DMA mode

SSPOL

SPI Chip Select Signal Polarity Control

0: Active high polarity (0 = Idle)

1: Active low polarity (1 = Idle)

POL

SPI Clock Polarity Control

0: Active high polarity (0 = Idle)

1: Active low polarity (1 = Idle)

PHA

SPI Clock/Data Phase Control

0: Phase 0 (Leading edge for sample data)

1: Phase 1 (Leading edge for setup data)

MODE

SPI Function Mode Select

Loading...

Loading...