A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 598 / 812

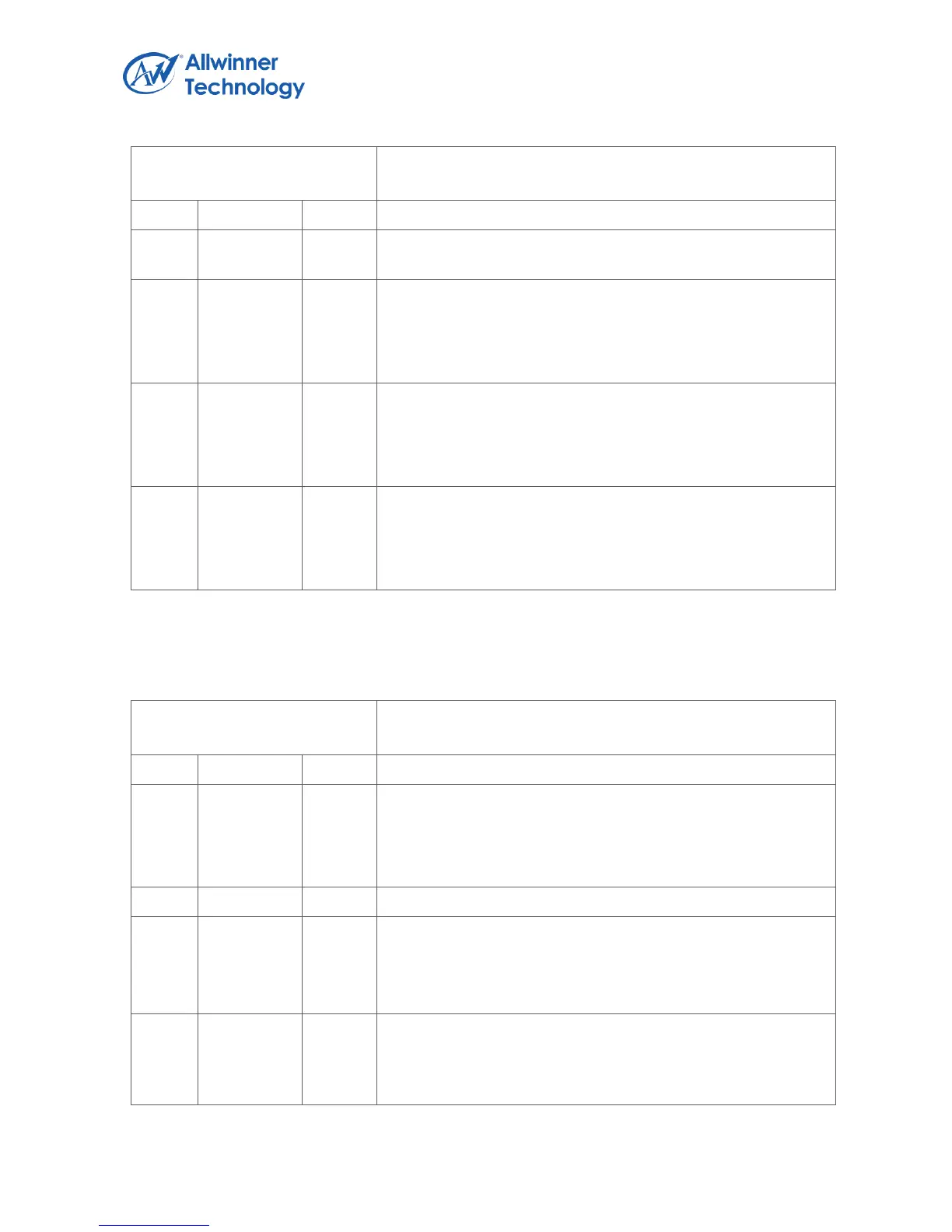

Register Name: SPI_INTCTL

Default Value: 0x0000_0000

RF_FU_INT_EN

RX FIFO Full Interrupt Enable

0: Disable

1: Enable

RF_HALF_FU_INT_EN

RX FIFO Half Full Interrupt Enable

0: Disable

1: Enable

RF_RDY_INT_EN

RX FIFO Ready Interrupt Enable

0: Disable

1: Enable

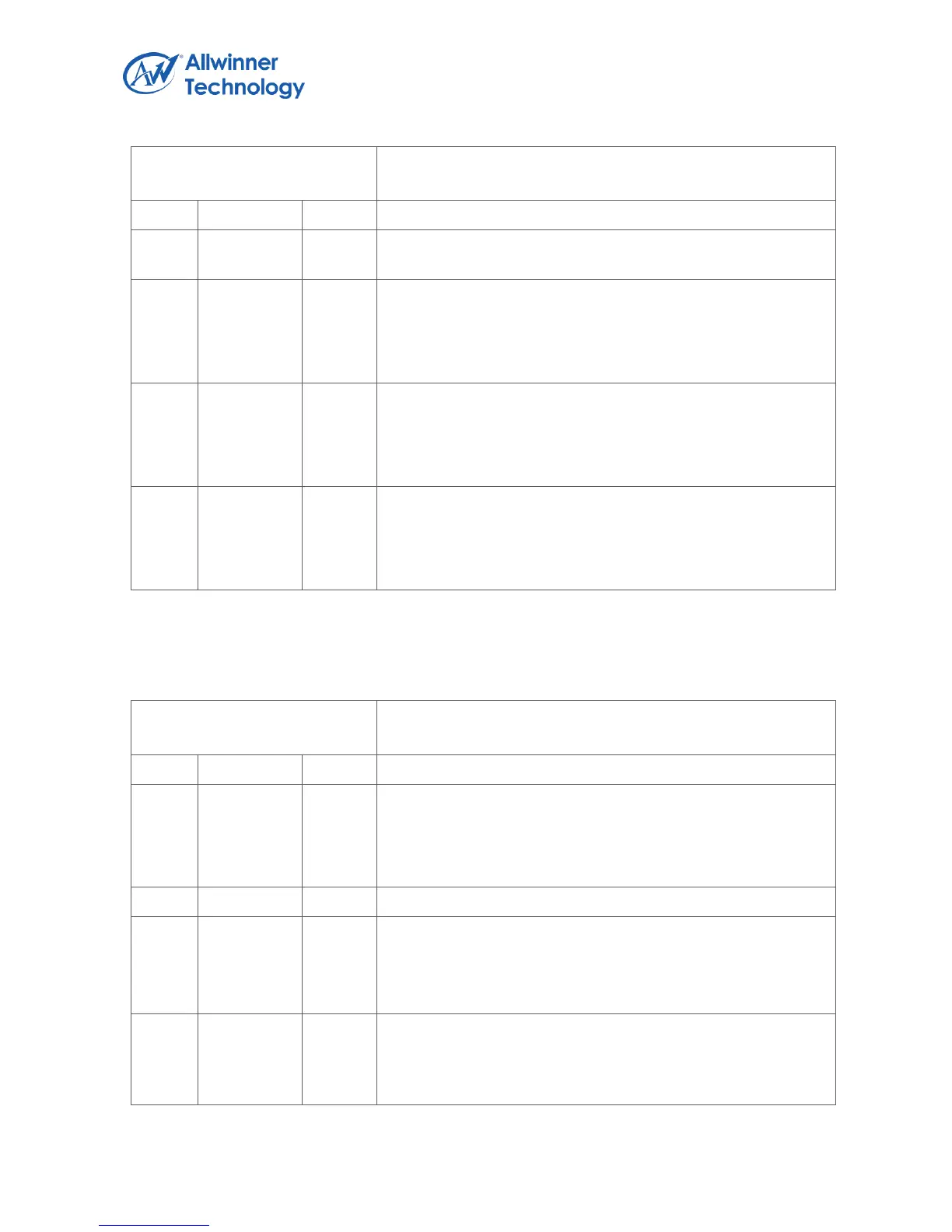

6.3.4.5. SPI INTERRUPT STATUS REGISTER

Register Name: SPI_INT_STA

Default Value: 0x0000_1B00

INT_CBF

Interrupt Clear Busy Flag

0: clear interrupt flag done

1; clear interrupt flag busy

SSI

SS Invalid Interrupt

When SSI is 1, it indicates that SS has changed from valid

state to invalid state. Writing 1 to this bit clears it.

TC

Transfer Completed

In master mode, it indicates that all bursts specified by BC has

been exchanged. In other condition, When set, this bit

Loading...

Loading...