A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 599 / 812

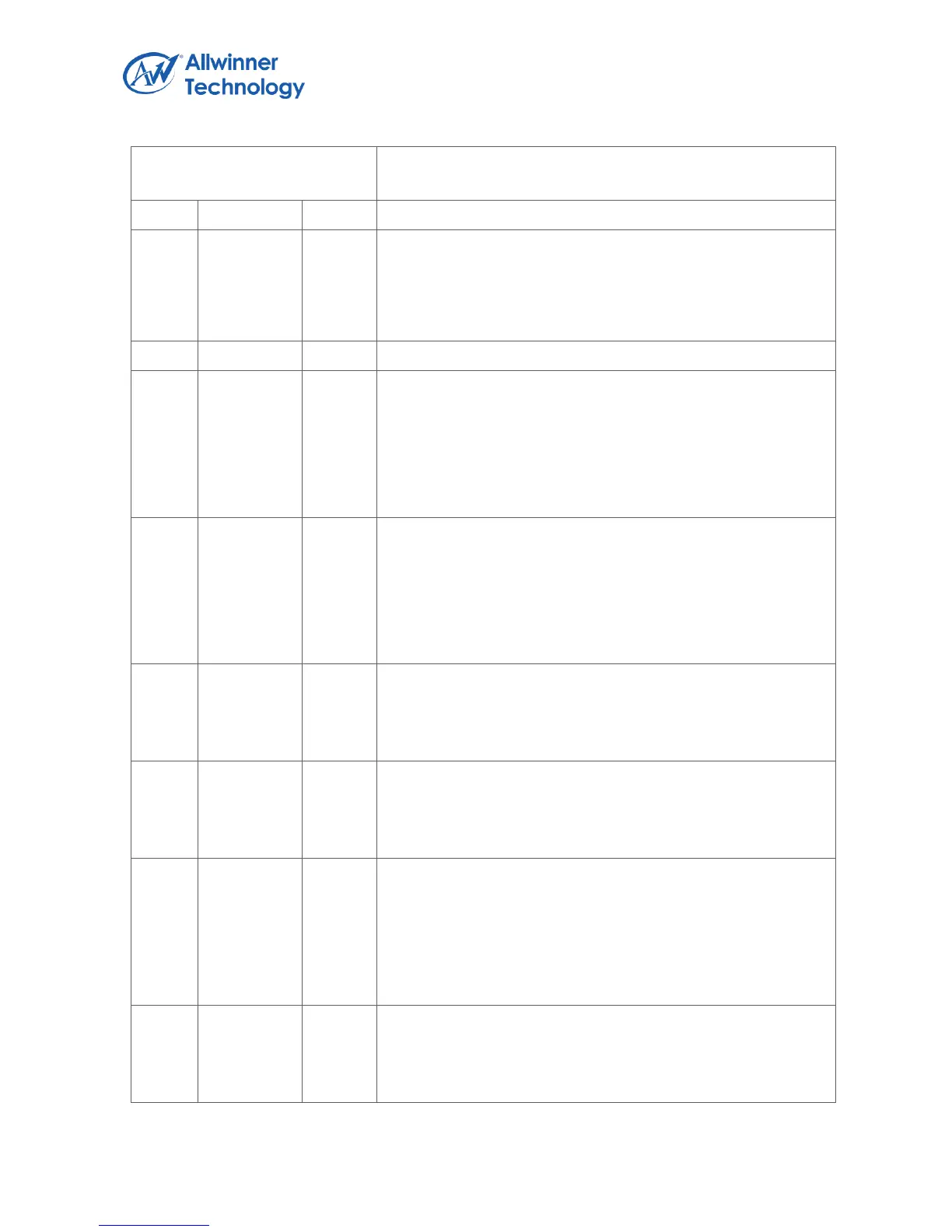

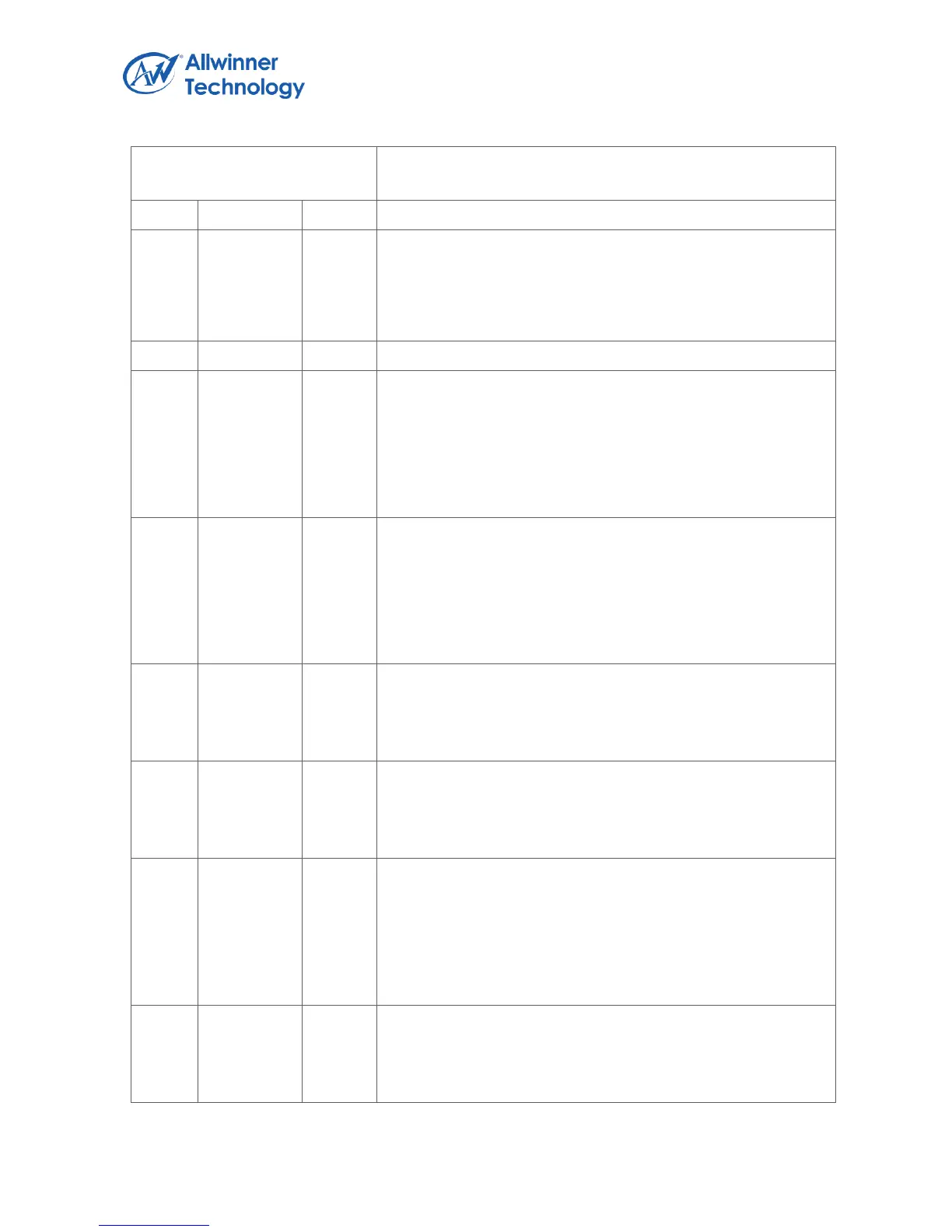

Register Name: SPI_INT_STA

Default Value: 0x0000_1B00

indicates that all the data in TXFIFO has been loaded in the

Shift register, and the Shift register has shifted out all the bits.

Writing 1 to this bit clears it.

0: Busy

1: Transfer Completed

TU

TXFIFO under run

This bit is set when if the TXFIFO is underrun. Writing 1 to this

bit clears it.

0: TXFIFO is not underrun

1: TXFIFO is underrun

TO

TXFIFO Overflow

This bit is set when if the TXFIFO is overflow. Writing 1 to this

bit clears it.

0: TXFIFO is not overflow

1: TXFIFO is overflowed

TE34

TXFIFO 3/4 empty

This bit is set if the TXFIFO is more than 3/4 empty. Writing 1

to this bit clears it.

TE14

TXFIFO 1/4 empty

This bit is set if the TXFIFO is more than 1/4 empty. Writing 1

to this bit clears it.

TF

TXFIFO Full

This bit is set when if the TXFIFO is full . Writing 1 to this bit

clears it.

0: TXFIFO is not Full

1: TXFIFO is Full

THE

TXFIFO Half empty

This bit is set if the TXFIFO is more than half empty. Writing 1

to this bit clears it.

Loading...

Loading...