A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 601 / 812

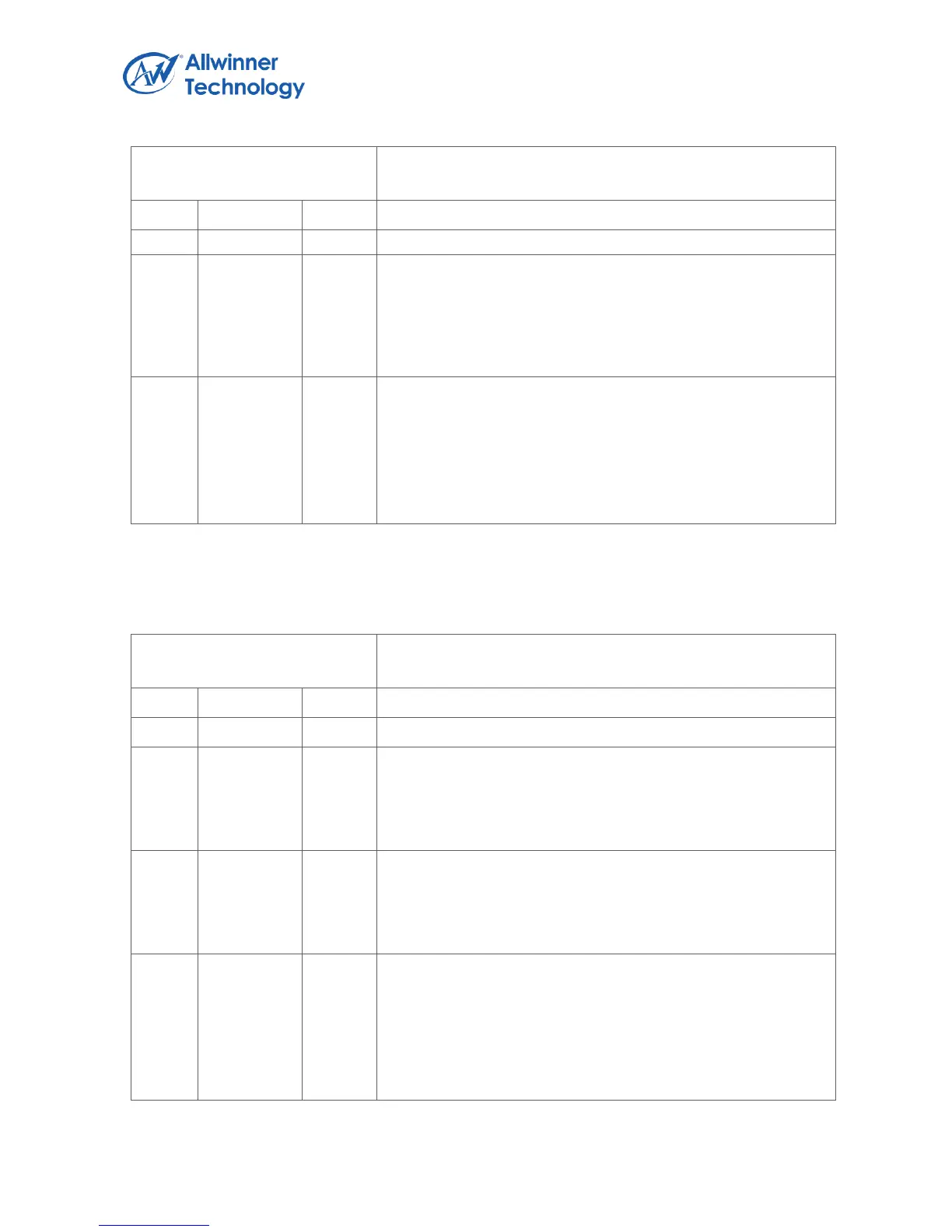

Register Name: SPI_INT_STA

Default Value: 0x0000_1B00

RHF

RXFIFO Half Full. This bit is set if the RXFIFO is half full (≥ 4

words in RXFIFO) . Writing 1 to this bit clears it.

0: Less than 4 words are stored in RXFIFO.

1: Four or more words are available in RXFIFO.

RR

RXFIFO Ready

This bit is set any time there is one or more words stored in

RXFIFO (≥ 1 words) . Writing 1 to this bit clears it.

0: No valid data in RXFIFO

1: More than 1 word in RXFIFO

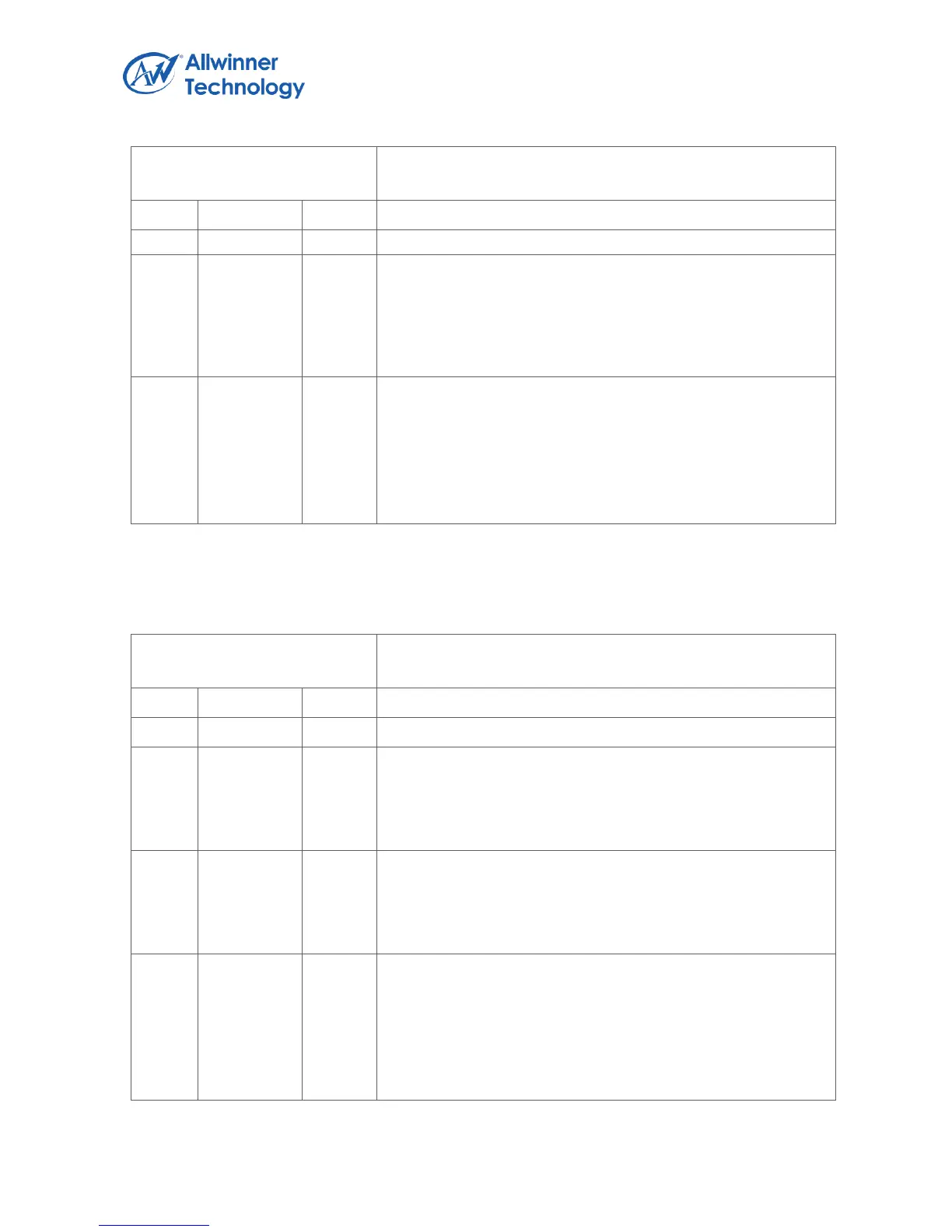

6.3.4.6. SPI DMA CONTROL REGISTER

Register Name: SPI_DMACTL

Default Value: 0x0000_0000

TF_EMP34_DMA

TXFIFO3/4 Empty DMA Request Enable

0: Disable

1: Enable

TF_EMP14_DMA

TXFIFO 1/4 Empty DMA Request Enable

0: Disable

1: Enable

TF_NF_DMA

TXFIFO Not Full DMA Request Enable

When enable, if more than one free room for burst, DMA

request is asserted, else de-asserted.

0: Disable

1: Enable

Loading...

Loading...