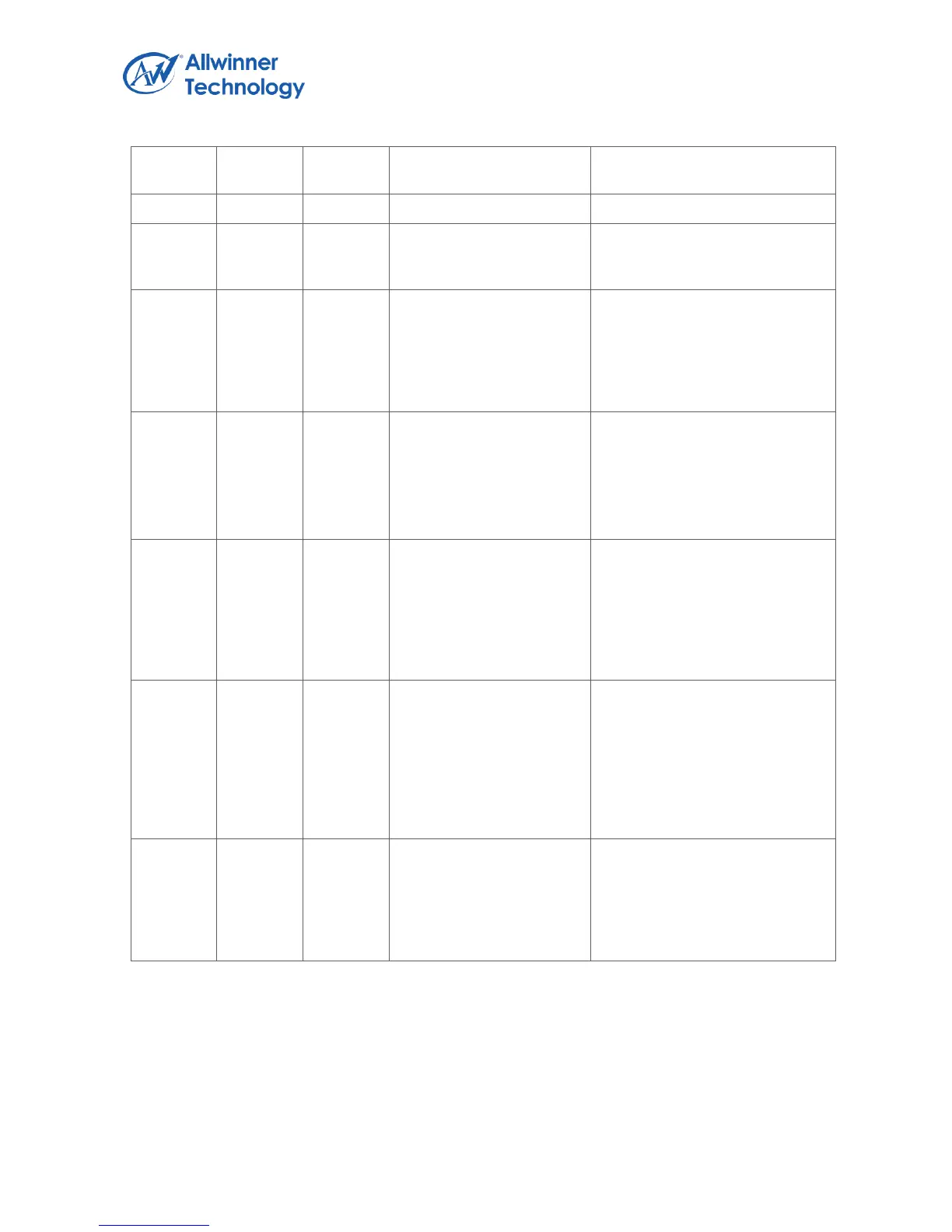

A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 614 / 812

Overrun/parity/ framing

errors or break interrupt

Reading the line status register

Receiver data available

(non-FIFO mode or FIFOs

disabled) or RCVR FIFO

trigger level reached

(FIFO mode and FIFOs

enabled)

Reading the receiver buffer

register (non-FIFO mode or

FIFOs disabled) or the FIFO

drops below the trigger level

(FIFO mode and FIFOs

enabled)

Characte

r timeout

indication

No characters in or out of

the RCVR FIFO during

the last 4 character times

and there is at least

1character in it during

This time

Reading the receiver buffer

register

Transmit

holding

register

empty

Transmitter holding

register empty (Program

THRE Mode disabled) or

XMIT FIFO at or below

threshold (Program THRE

Mode enabled)

Reading the IIR register (if

source of interrupt); or, writing

into THR (FIFOs or THRE Mode

not selected or disabled) or

XMIT FIFO above threshold

(FIFOs and THRE Mode

selected and enabled).

Clear to send or data set

ready or ring indicator or

data carrier detect. Note

that if auto flow control

mode is enabled, a

change in CTS (that is,

DCTS set) does not

cause an interrupt.

Reading the Modem status

Register

UART_16550_COMPATI

BLE = NO and master

has tried to write to the

Line Control Register

while the UART is busy

(USR[0] is set to one).

Reading the UART status

register

Loading...

Loading...