A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 615 / 812

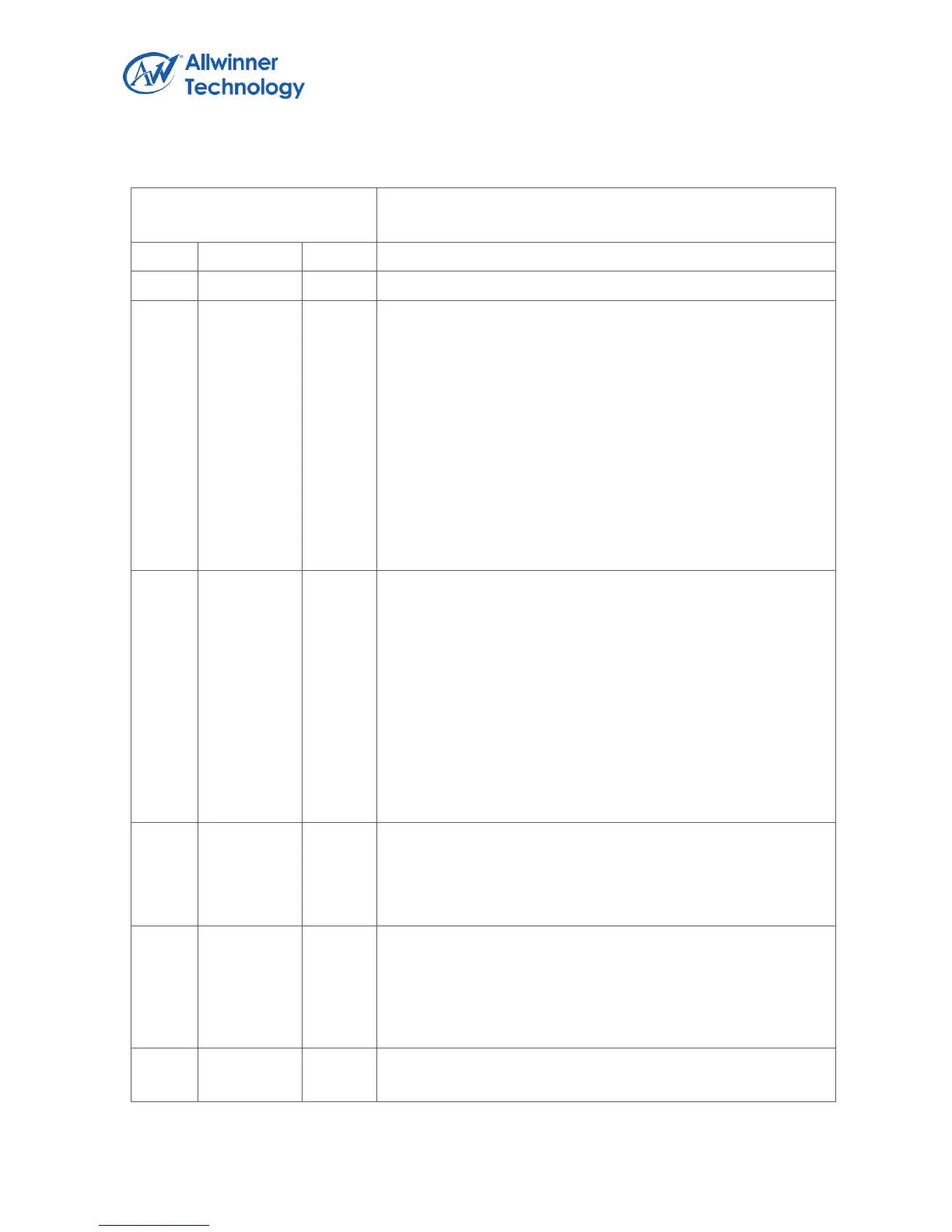

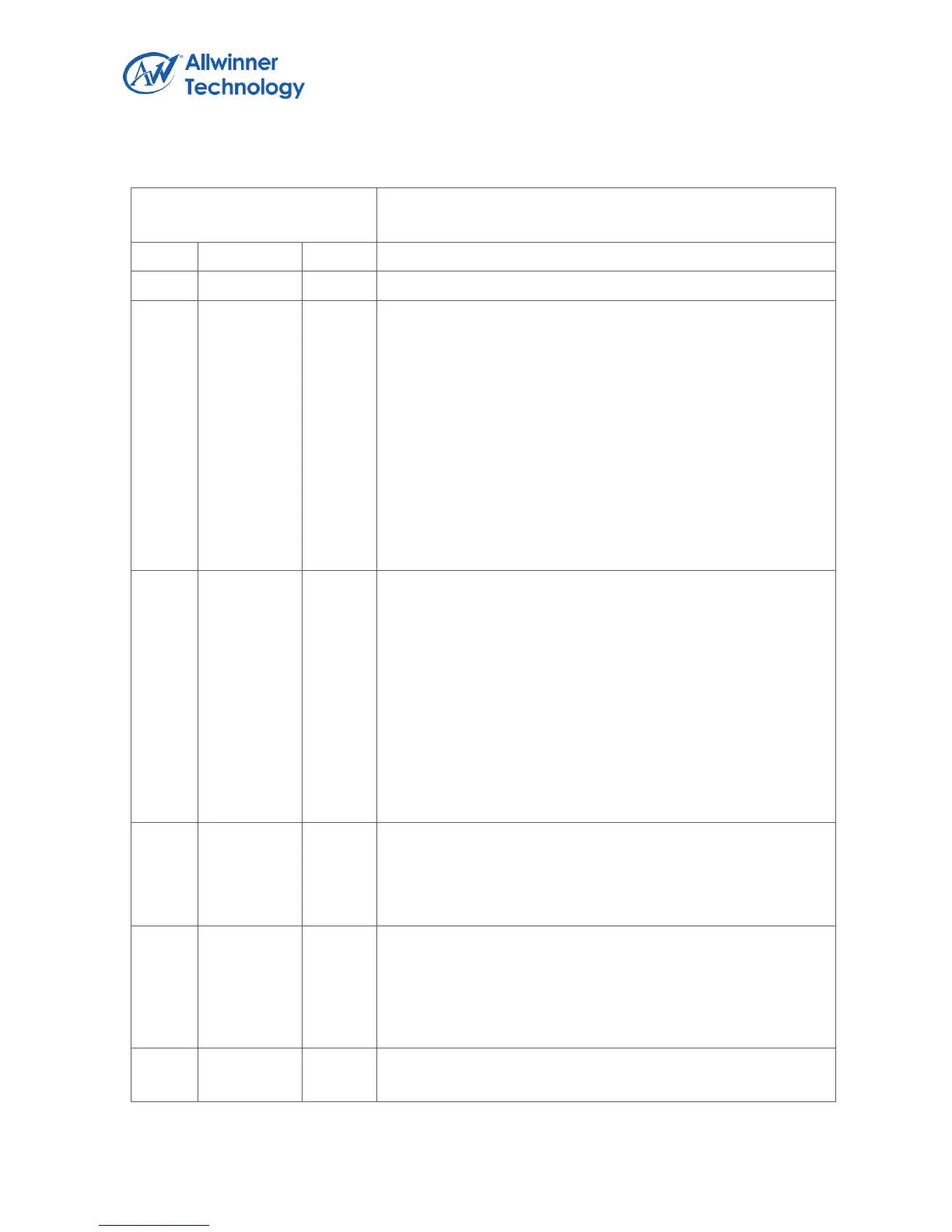

6.4.4.7. UART FIFO CONTROL REGISTER

Register Name: UART_FCR

Default Value: 0x0000_0000

RT

RCVR Trigger

This is used to select the trigger level in the receiver FIFO at

which the Received Data Available Interrupt is generated. In

auto flow control mode it is used to determine when the rts_n

signal is de-asserted. It also determines when the

dma_rx_req_n signal is asserted in certain modes of

operation.

00: 1 character in the FIFO

01: FIFO ¼ full

10: FIFO ½ full

11: FIFO-2 less than full

TFT

TX Empty Trigger

Writes have no effect when THRE_MODE_USER = Disabled.

This is used to select the empty threshold level at which the

THRE Interrupts are generated when the mode is active. It

also determines when the dma_tx_req_n signal is asserted

when in certain modes of operation.

00: FIFO empty

01: 2 characters in the FIFO

10: FIFO ¼ full

11: FIFO ½ full

DMAM

DMA Mode

0: Mode 0

1: Mode 1

XFIFOR

XMIT FIFO Reset

This resets the control portion of the transmit FIFO and treats

the FIFO as empty. This also de-asserts the DMA TX request.

It is ‘self-clearing’. It is not necessary to clear this bit.

Loading...

Loading...