A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 618 / 812

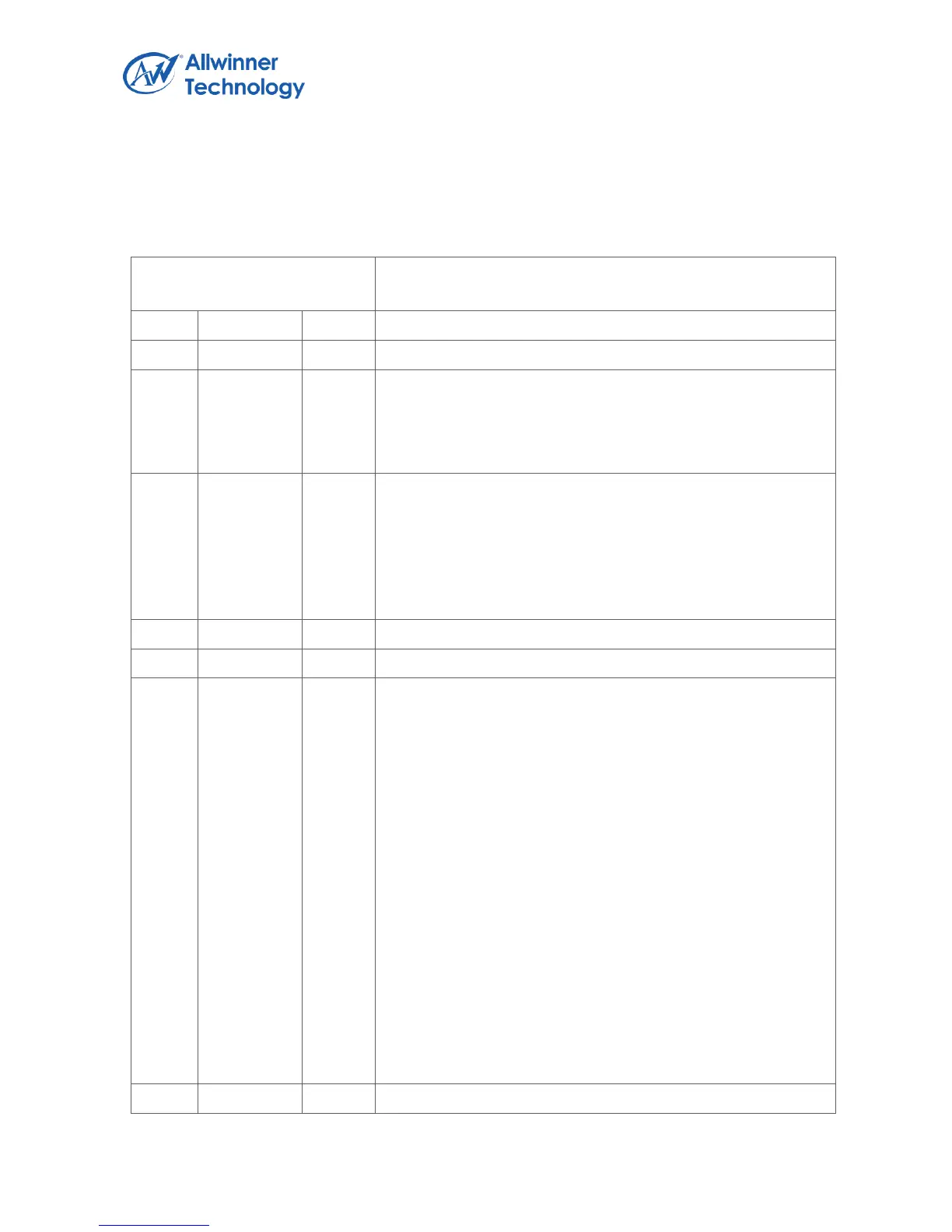

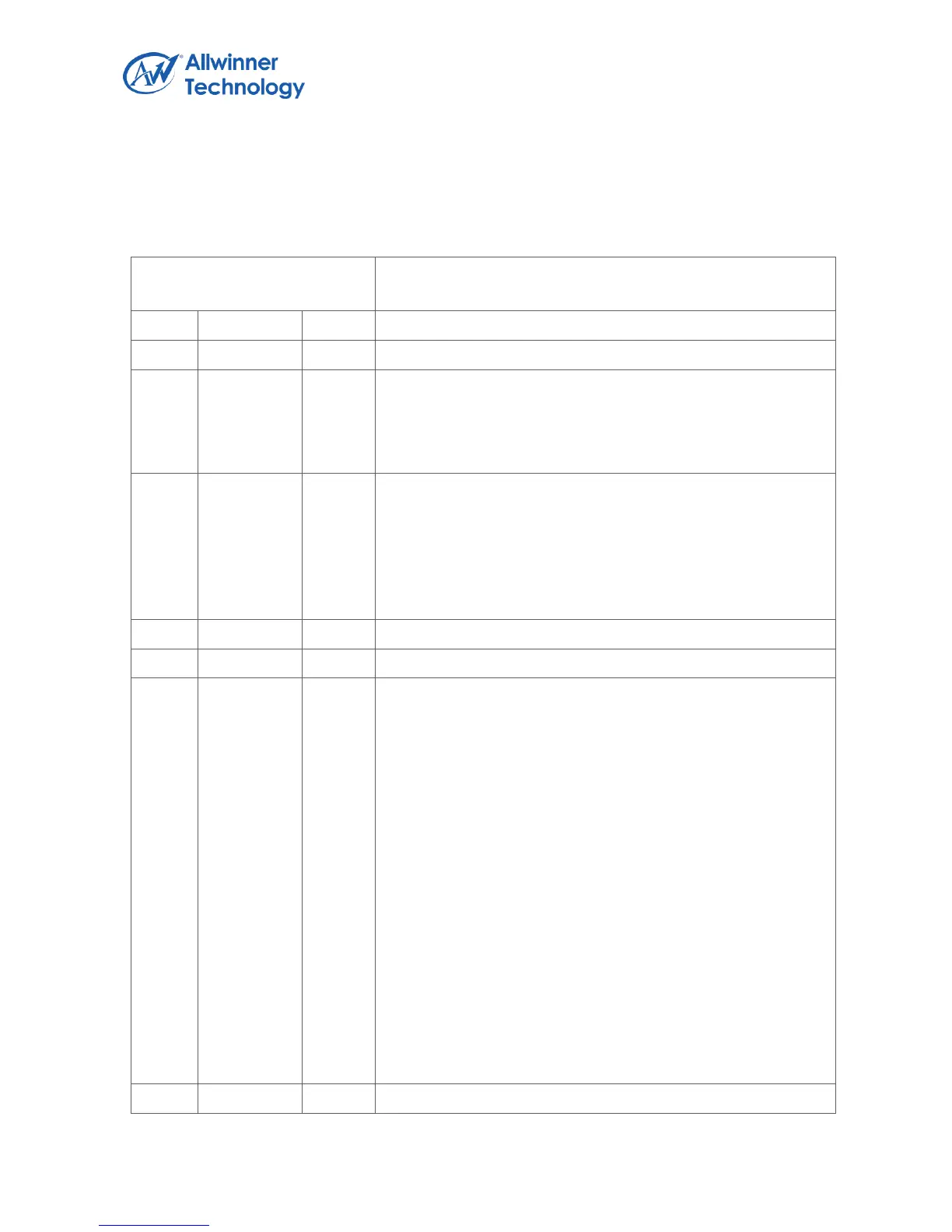

6.4.4.9. UART MODEM CONTROL REGISTER

AFCE

Auto Flow Control Enable

When FIFOs are enabled and the Auto Flow Control Enable

(AFCE) bit is set, Auto Flow Control features are enabled.

0: Auto Flow Control Mode disabled

1: Auto Flow Control Mode enabled

RTS

Request to Send

This is used to directly control the Request to Send (rts_n)

output. The Request To Send (rts_n) output is used to inform

the modem or data set that the UART is ready to exchange

data. When Auto RTS Flow Control is not enabled (MCR[5] set

to zero), the rts_n signal is set low by programming MCR[1]

(RTS) to a high.In Auto Flow Control, AFCE_MODE ==

Enabled and active (MCR[5] set to one) and FIFOs enable

(FCR[0] set to one), the rts_n output is controlled in the same

way, but is also gated with the receiver FIFO threshold trigger

(rts_n is

inactive high when above the threshold). The rts_n signal is

de-asserted when MCR[1] is set low.

0: rts_n de-asserted (logic 1)

1: rts_n asserted (logic 0)

Note that in Loopback mode (MCR[4] set to one), the rts_n

output is held inactive high while the value of this location is

internally looped back to an input.

Loading...

Loading...