A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 619 / 812

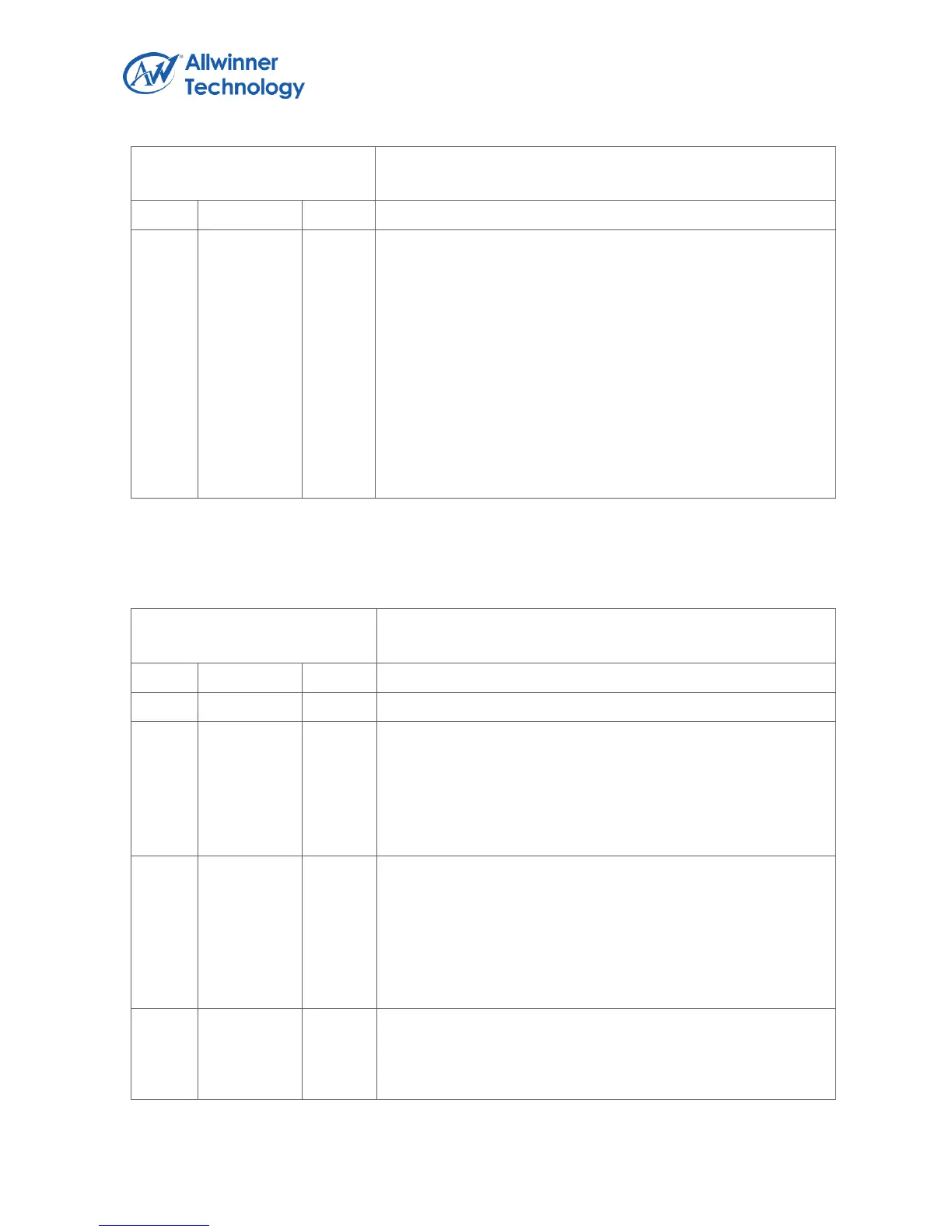

Register Name: UART_MCR

Default Value: 0x0000_0000

Data Terminal Ready

This is used to directly control the Data Terminal Ready (dtr_n)

output. The value written to this location is inverted and driven

out on dtr_n

。」

0:dtr_n de-asserted (logic 1)

1:dtr_n asserted (logic 0)

The Data Terminal Ready output is used to inform the modem

or data set that the UART is ready to establish

communications.

Note that in Loopback mode (MCR[4] set to one), the dtr_n

output is held inactive high while the value of this location is

internally looped back to an input.

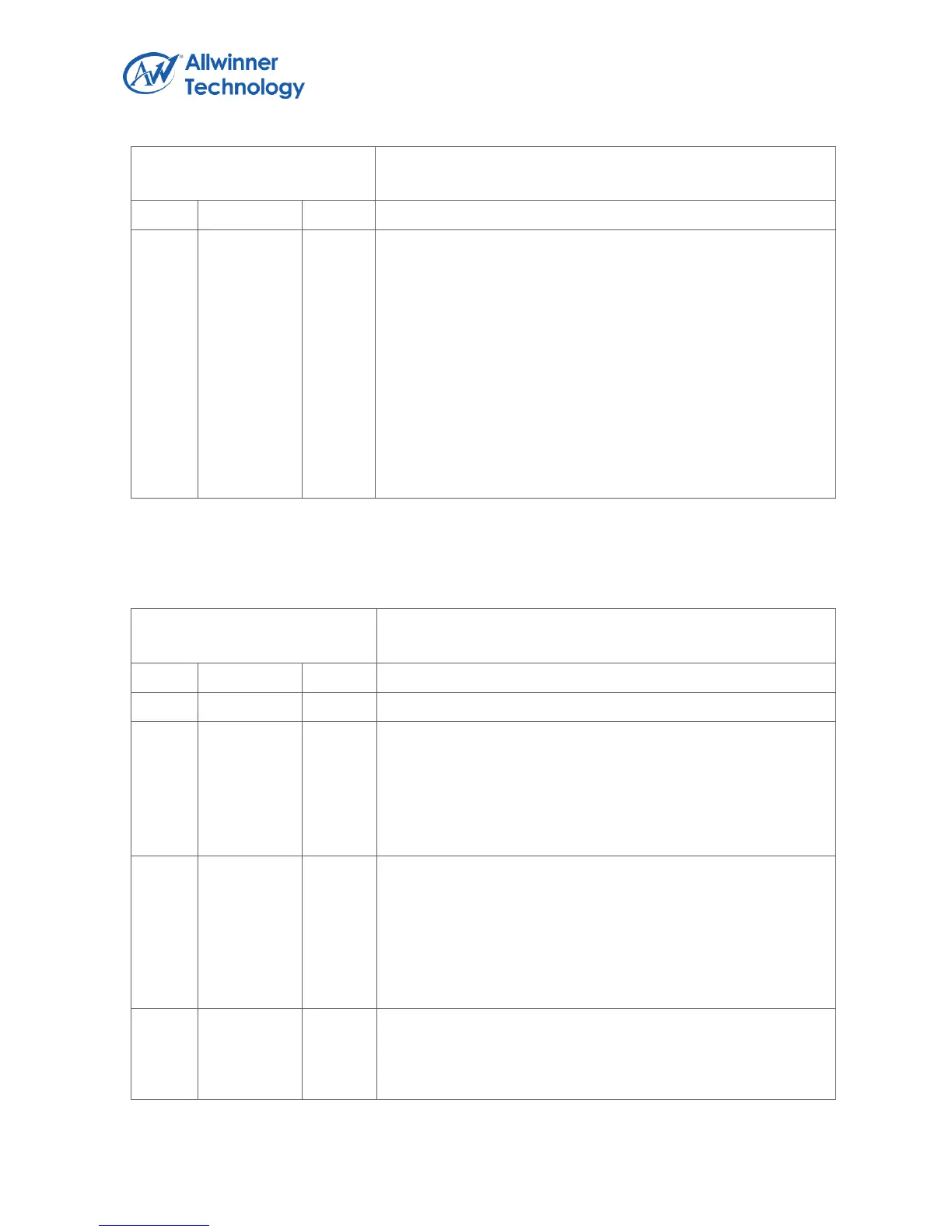

6.4.4.10. UART LINE STATUS REGISTER

Register Name: UART_LSR

Default Value: 0x0000_0060

FIFOERR

RX Data Error in FIFO

When FIFOs are disabled, this bit is always 0. When FIFOs

are enabled, this bit is set to 1 when there is at least one PE,

FE, or BI in the RX FIFO. It is cleared by a read from the LSR

register provided there are no subsequent errors in the FIFO.

TEMT

Transmitter Empty

If the FIFOs are disabled, this bit is set to "1" whenever the TX

Holding Register and the TX Shift Register are empty. If the

FIFOs are enabled, this bit is set whenever the TX FIFO and

the TX Shift Register are empty. In both cases, this bit is

cleared when a byte is written to the TX data channel.

THRE

TX Holding Register Empty

If the FIFOs are disabled, this bit is set to “1” whenever the TX

Holding Register is empty and ready to accept new data and it

Loading...

Loading...