A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 649 / 812

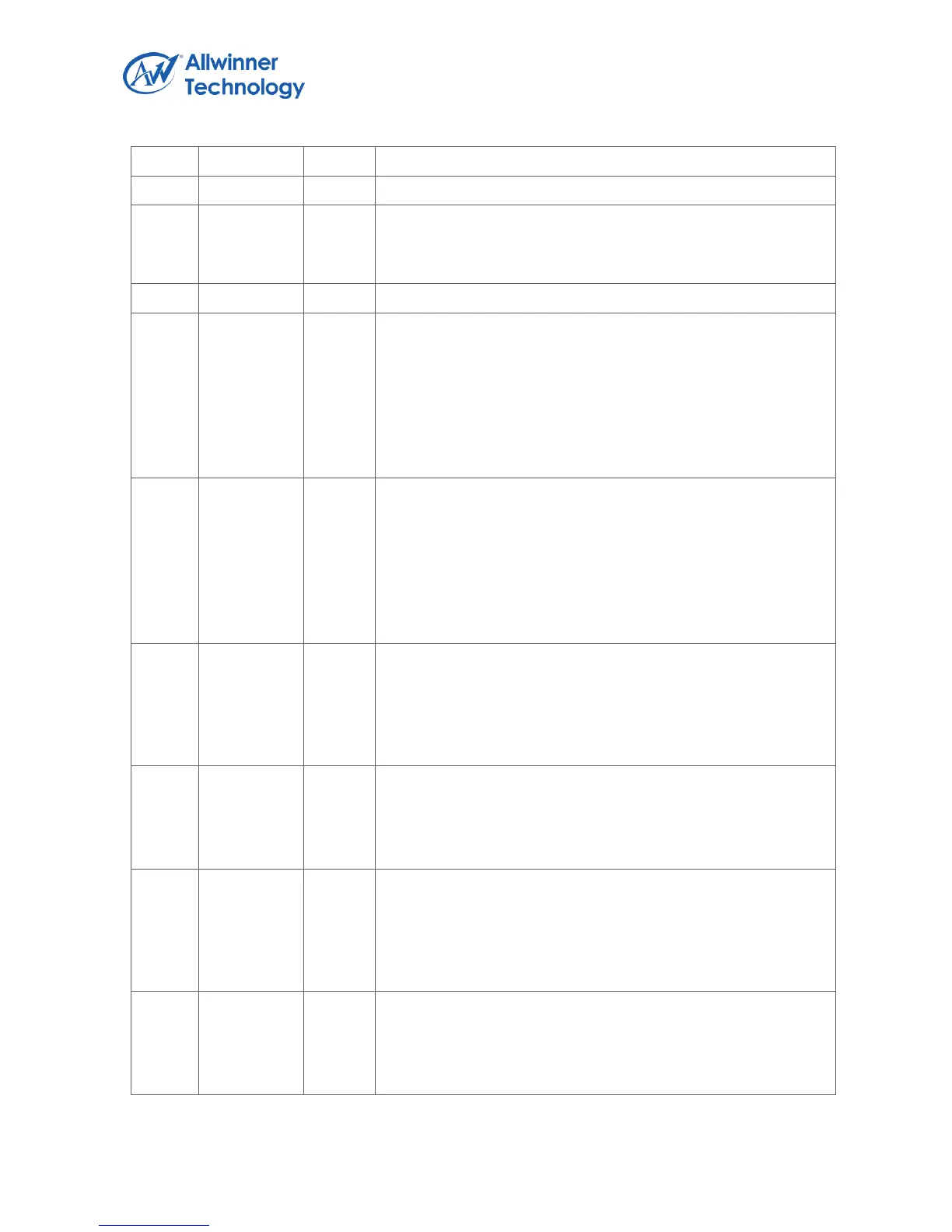

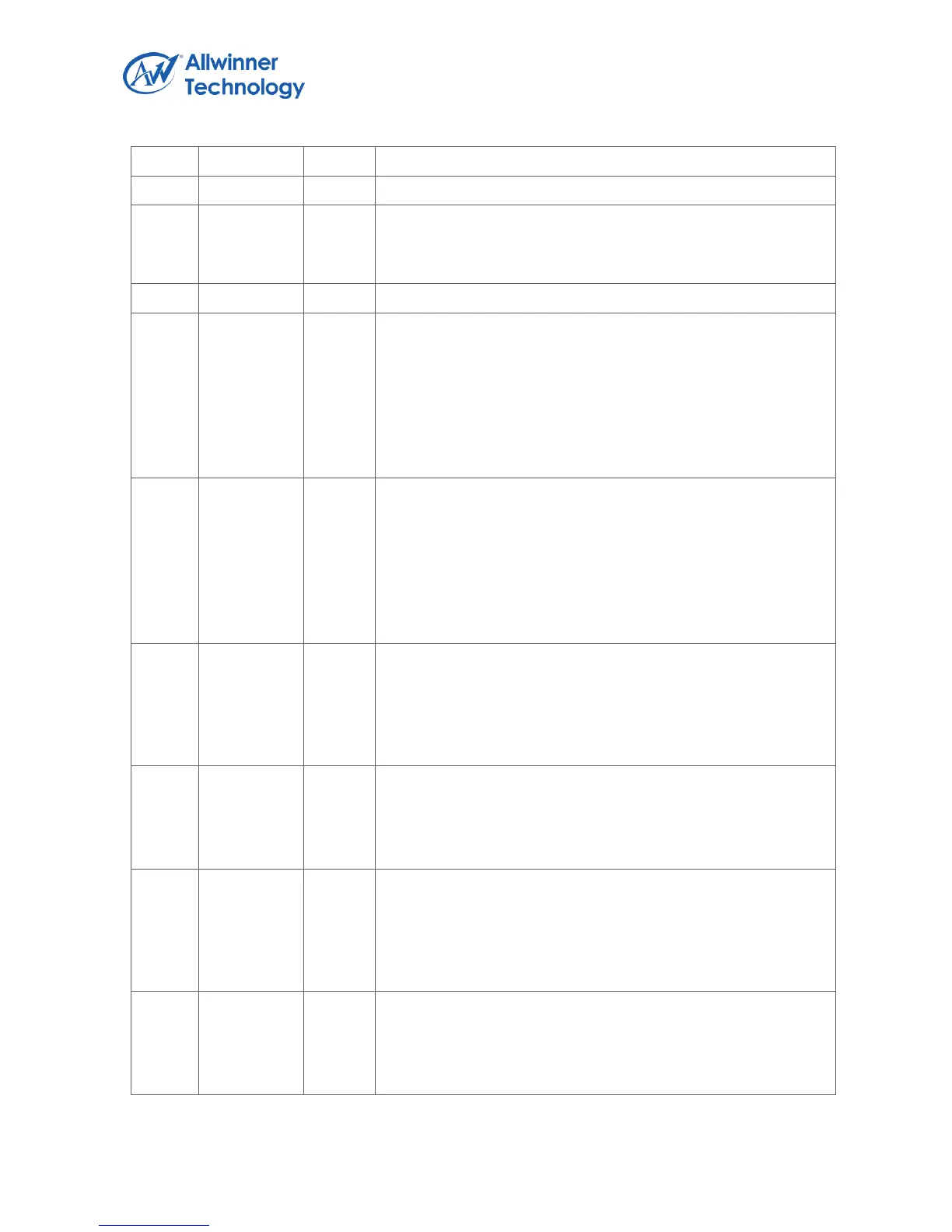

TEL

TX FIFO Empty Level for interrupt and DMA request

TRIGGER_LEVEL = TEL + 1

DRQ_EN

TX FIFO Empty DMA Enable

0: Disable

1: Enable

When set to ‘1’, the Transmitter FIFO DRQ is asserted if

reaching TEL. The DRQ is de-asserted when condition fails or

specified number data has been sent from host CPU.

TEI_EN

TX FIFO Empty Interrupt Enable

0: Disable

1: Enable

When set to ‘1’, the Transmitter FIFO interrupt is asserted if

reaching TEL. The interrupt is de-asserted when condition fails

or specified number data has been sent from host CPU.

TCI_EN

Transmit (including the CRC and STO fields) Complete

Interrupt Enable

0: Disable

1: Enable

SIPEI_EN

Transmitter SIP End Interrupt Enable

0: Disable

1: Enable

TPEI_EN

Transmitter Packet (the address, control and data fields) End

Interrupt Enable

0: Disable

1: Enable

TUI_EN

Transmitter FIFO Under run Interrupt Enable

0: Disable

1: Enable

Loading...

Loading...