A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 651 / 812

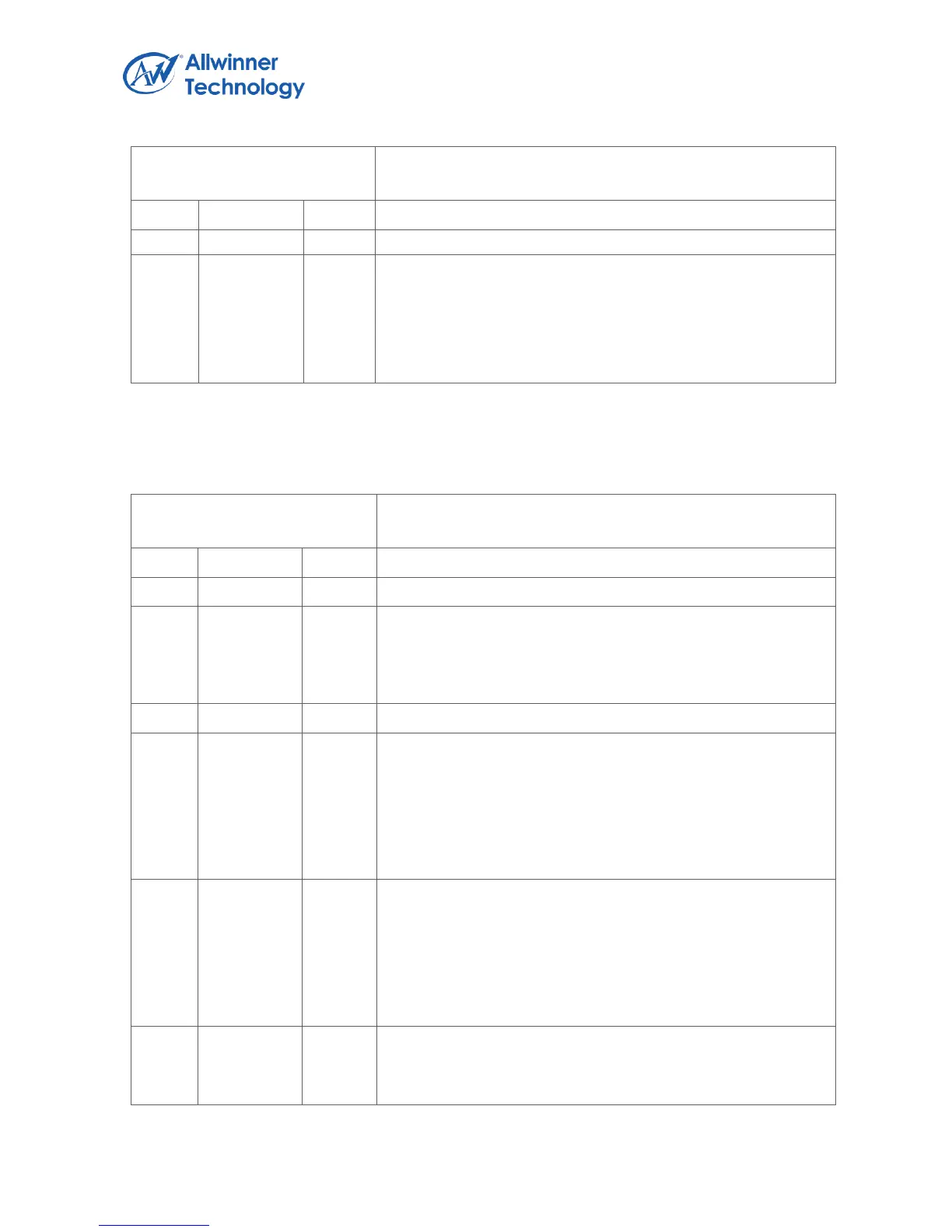

Register Name: IR_TXSTA

Default Value: 0x0000_1000

This bit is cleared by writing a ‘1’.

TU

Transmitter FIFO Under Run

0: No transmitter FIFO under run

1: Transmitter FIFO under run

This bit is cleared by writing a ‘1’.

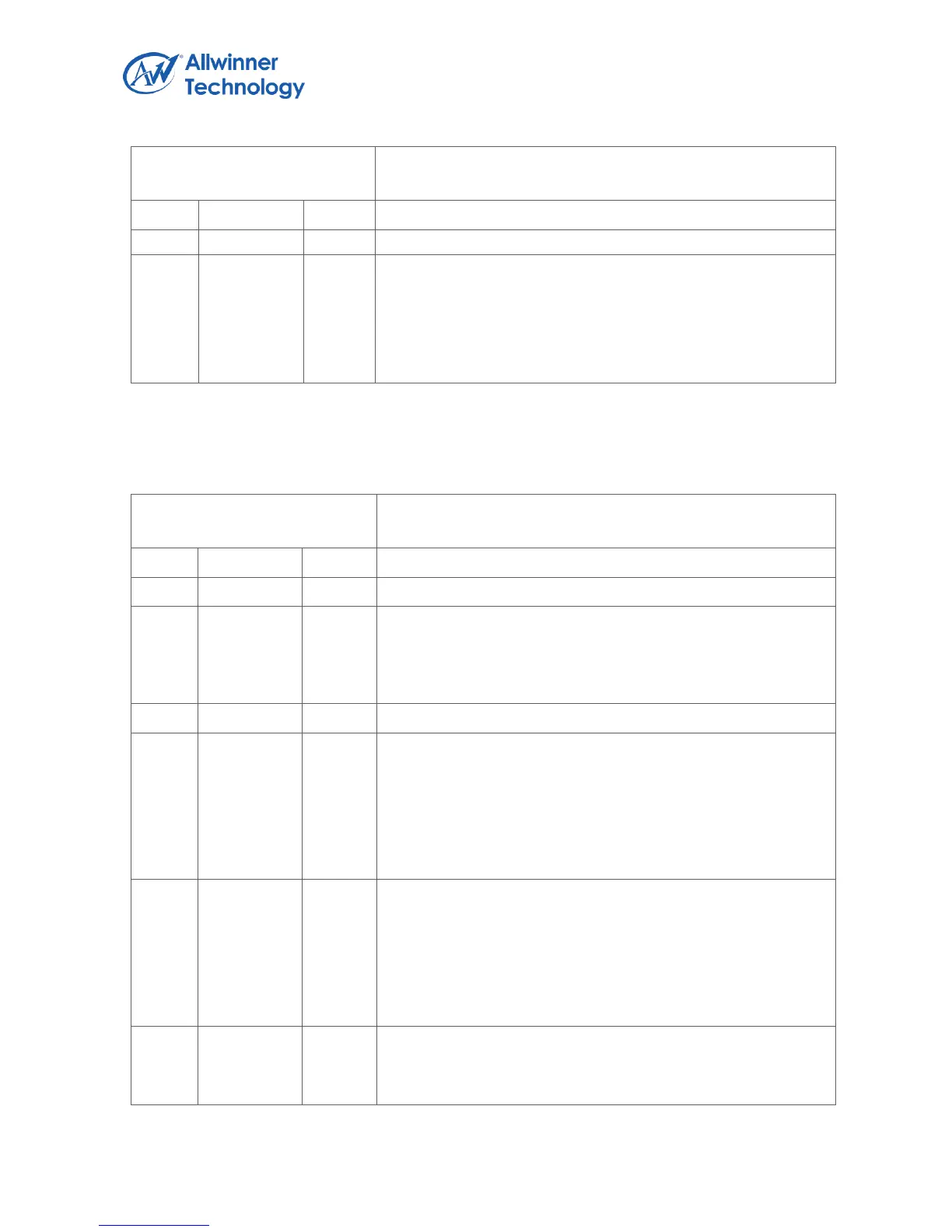

6.6.3.12. IR RECEIVER INTERRUPT CONTROL REGISTER

Register Name: IR_RXINT

Default Value: 0x0000_0000

RAL

RX FIFO Available Received Byte Level for interrupt and DMA

request

TRIGGER_LEVEL = RAL + 1

DRQ_EN

RX FIFO DMA Enable

0: Disable

1: Enable

When set to ‘1’, the Receiver FIFO DRQ is asserted if

reaching RAL. The DRQ is de-asserted when condition fails.

RAI_EN

RX FIFO Available Interrupt Enable

0: Disable

1: Enable

When set to ‘1’, the Receiver FIFO IRQ is asserted if reaching

RAL. The IRQ is de-asserted when condition fails.

CRCI_EN

Receiver CRC Error Interrupt Enable

0: Disable

Loading...

Loading...