A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 668 / 812

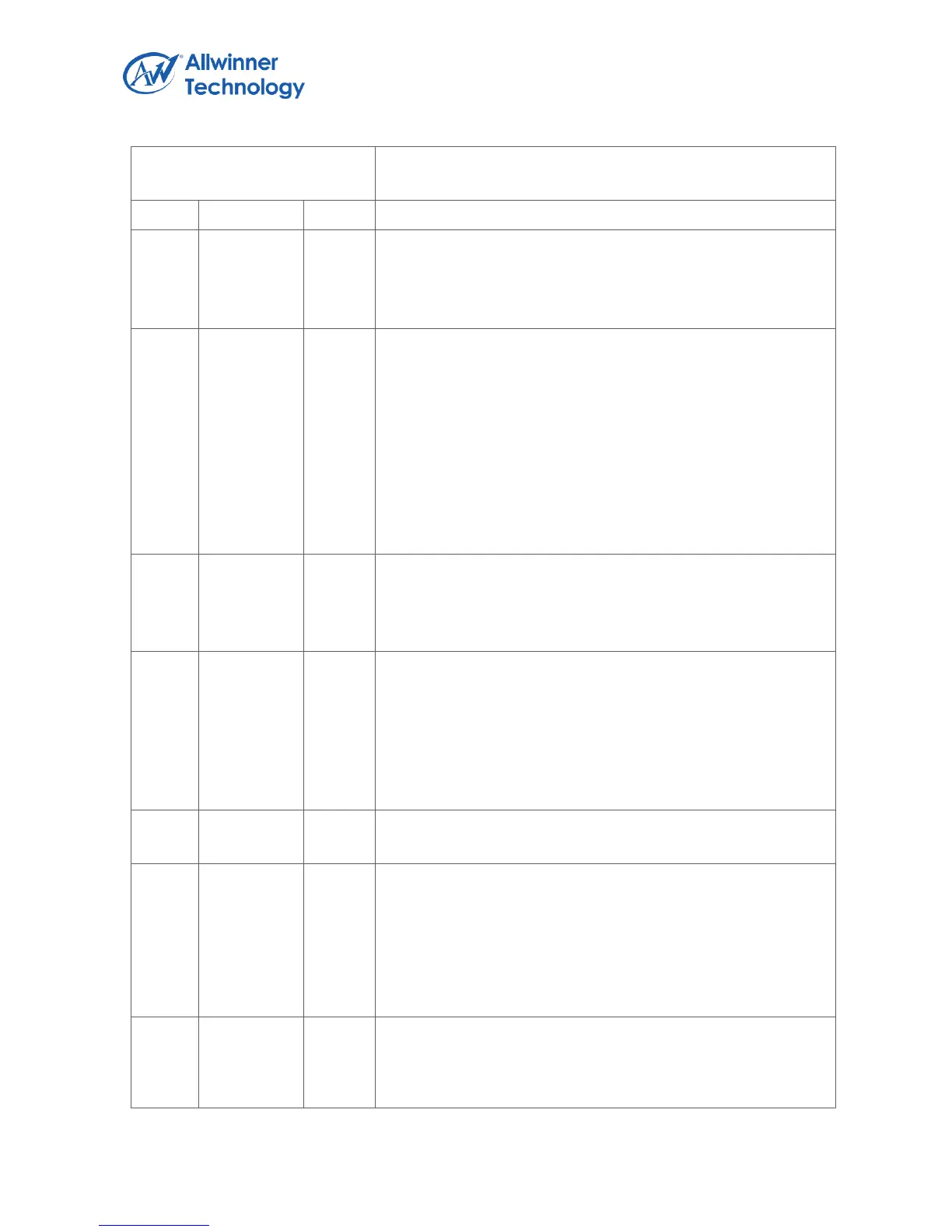

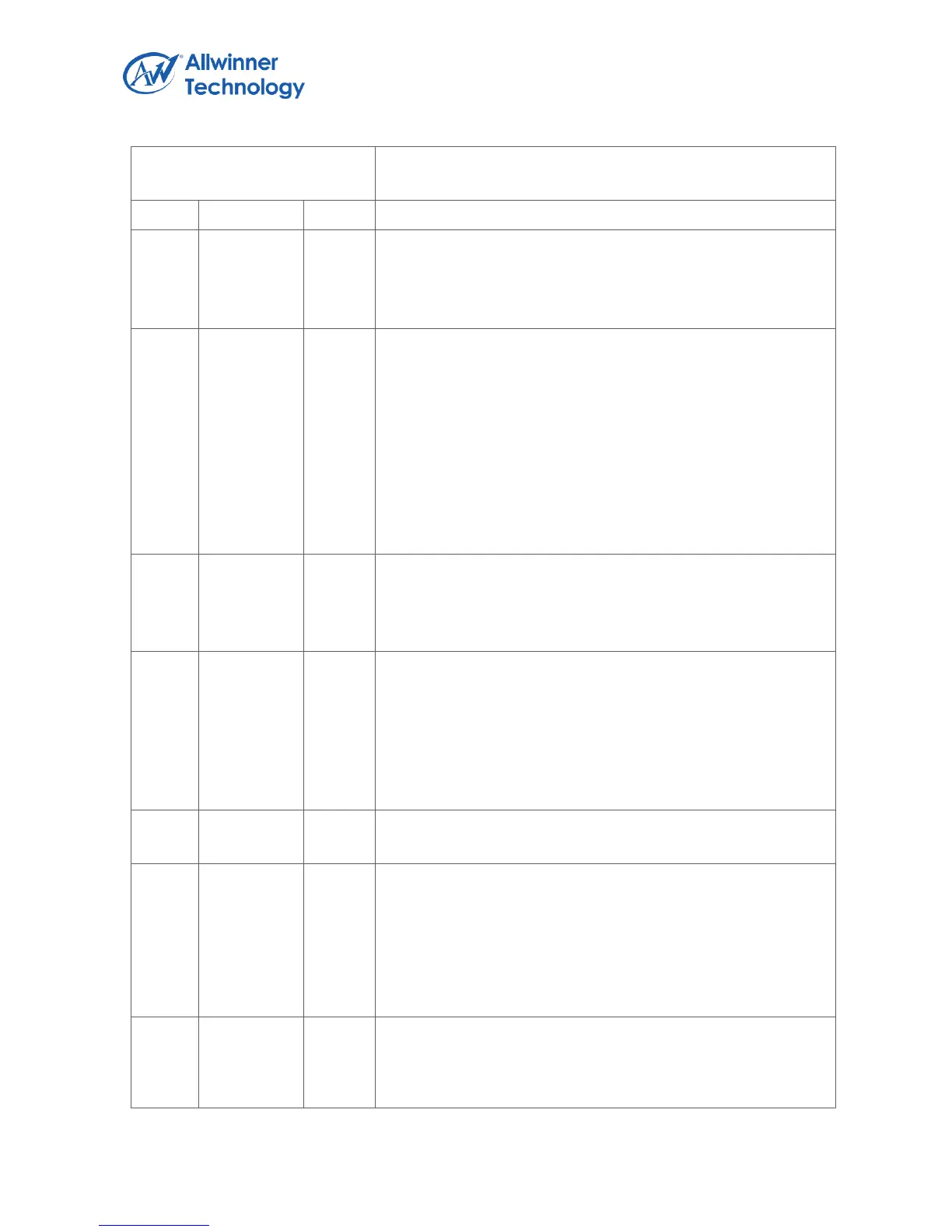

Register Name: USBSTS

Default Value: 0x00001000

Asynchronous Schedule when software transitions the

Asynchronous Schedule Enable bit in the USBCMD register.

When this bit and the Asynchronous Schedule Enable bit are

the same value, the Asynchronous Schedule is either enabled

(1) or disabled (0).

PSS

Periodic Schedule Status

The bit reports the current real status of the Periodic Schedule.

If this bit is a zero then the status of the Periodic Schedule is

disabled. If this bit is a one then the status of the Periodic

Schedule is enabled. The Host Controller is not required to

immediately disable or enable the Periodic Schedule when

software transitions the Periodic Schedule Enable bit in the

USBCMD register. When this bit and the Periodic Schedule

Enable bit are the same value, the Periodic Schedule is either

enabled (1) or disabled (0).

RECL

Reclamation

This is a read-only status bit, which is used to detect an empty

asynchronous schedule.

HCH

HC Halted

This bit is a zero whenever the Run/Stop bit is a one. The Host

Controller Sets this bit to one after it has stopped executing as

a result of the Run/Stop bit being set to 0, either by software or

by the Host Controller Hardware (e.g. internal error).

The default value is ‘1’.

Reserved

These bits are reserved and should be set to zero.

IAA

Interrupt on Async Advance

System software can force the host controller to issue an

interrupt the next time the host controller advances the

asynchronous schedule by writing a one to the Interrupt on

Async Advance Doorbell bit in the USBCMD register. This

status bit indicates the assertion of that interrupt source.

HSE

Host System Error

The Host Controller set this bit to 1 when a serious error

occurs during a host system access involving the Host

Loading...

Loading...