A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 670 / 812

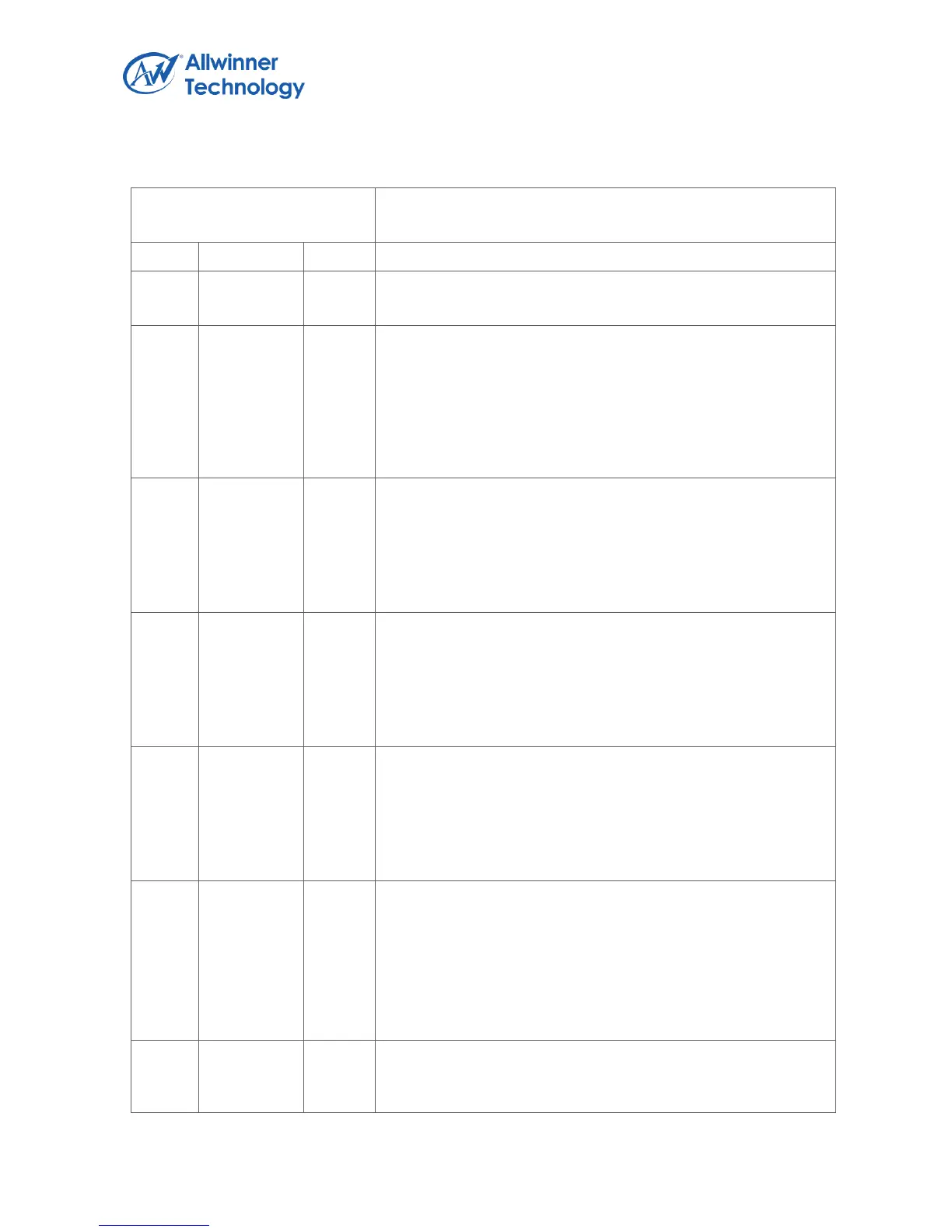

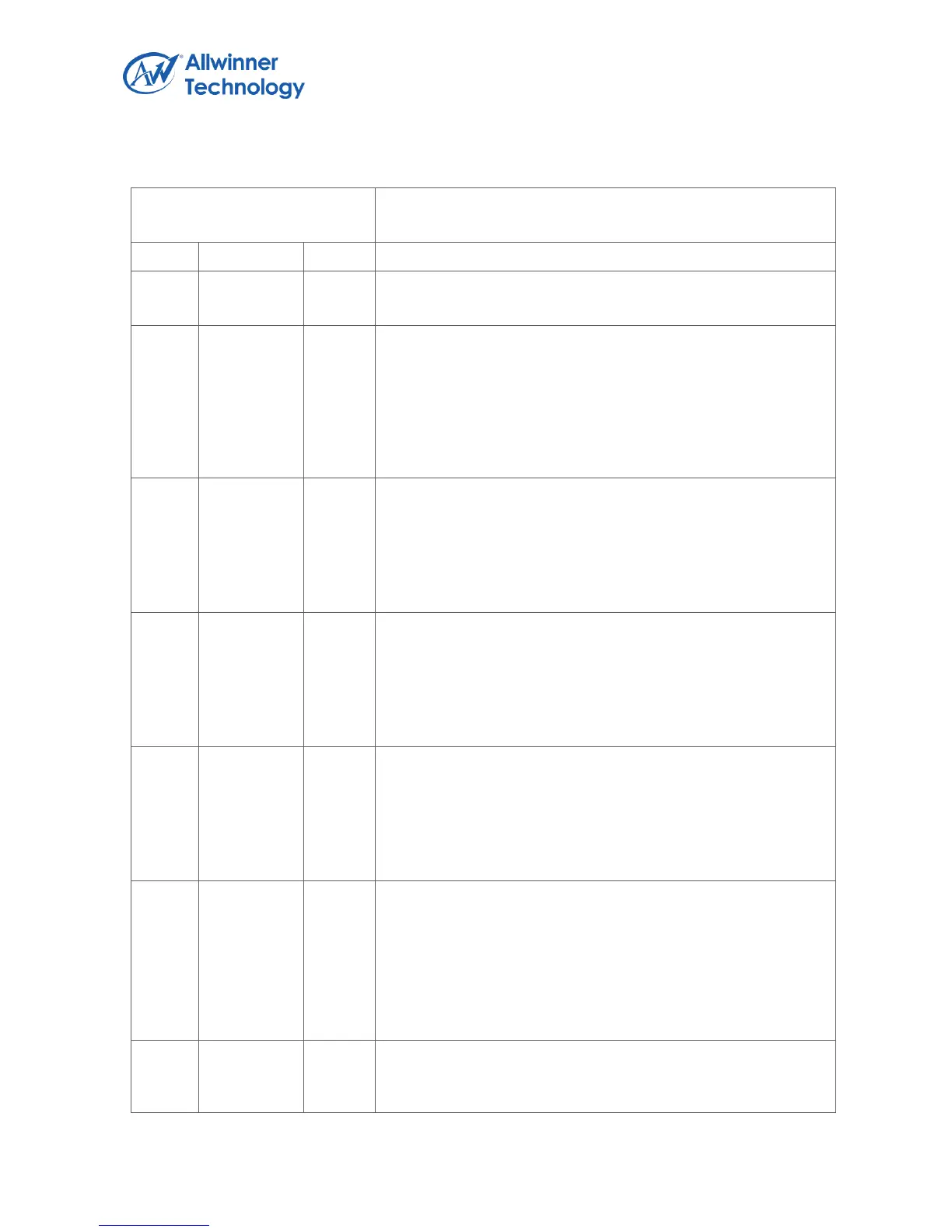

6.8.5.8. EHCI USB INTERRUPT ENABLE REGISTER

Register Name: USBINTR

Default Value:0x00000000

Reserved

These bits are reserved and should be zero.

IAAE

Interrupt on Async Advance Enable

When this bit is 1, and the Interrupt on Async Advance bit in

the USBSTS register is 1, the host controller will issue an

interrupt at the next interrupt threshold. The interrupt is

acknowledged by software clearing the Interrupt on Async

Advance bit.

HSEE

Host System Error Enable

When this bit is 1, and the Host System Error Status bit in the

USBSTS register is 1, the host controller will issue an interrupt.

The interrupt is acknowledged by software clearing the Host

System Error bit.

FLRE

Frame List Rollover Enable

When this bit is 1, and the Frame List Rollover bit in the

USBSTS register is 1, the host controller will issue an interrupt.

The interrupt is acknowledged by software clearing the Frame

List Rollover bit.

PCIE

Port Change Interrupt Enable

When this bit is 1, and the Port Chang Detect bit in the

USBSTS register is 1, the host controller will issue an interrupt.

The interrupt is acknowledged by software clearing the Port

Chang Detect bit.

EIE

USB Error Interrupt Enable

When this bit is 1, and the USBERRINT bit in the USBSTS

register is 1,the host controller will issue an interrupt at the

next interrupt threshold.

The interrupt is acknowledged by software clearing the

USBERRINT bit.

UIE

USB Interrupt Enable

When this bit is 1, and the USBINT bit in the USBSTS register

Loading...

Loading...