A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 710 / 812

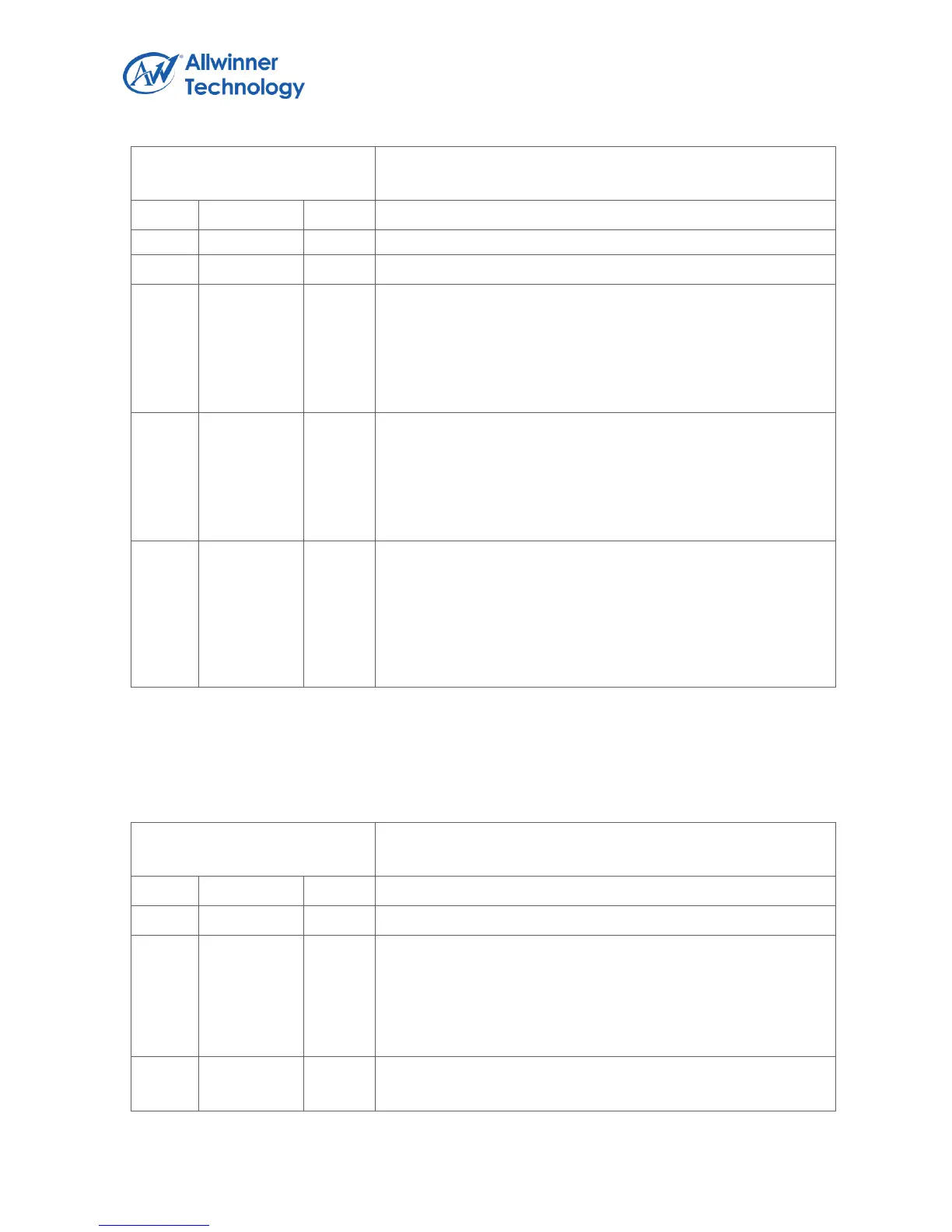

Register Name: DA_ISTA

Default Value: 0x0000_0010

RXU_INT

RX FIFO Under run Pending Interrupt

0: No Pending Interrupt

1:FIFO Under run Pending Interrupt

Write 1 to clear this interrupt

RXO_INT

RX FIFO Overrun Pending Interrupt

0: No Pending IRQ

1: FIFO Overrun Pending IRQ

Write ‘1’ to clear this interrupt

RXA_INT

RX FIFO Data Available Pending Interrupt

0: No Pending IRQ

1: Data Available Pending IRQ

Write ‘1’ to clear this interrupt or automatic clear if interrupt

condition fails.

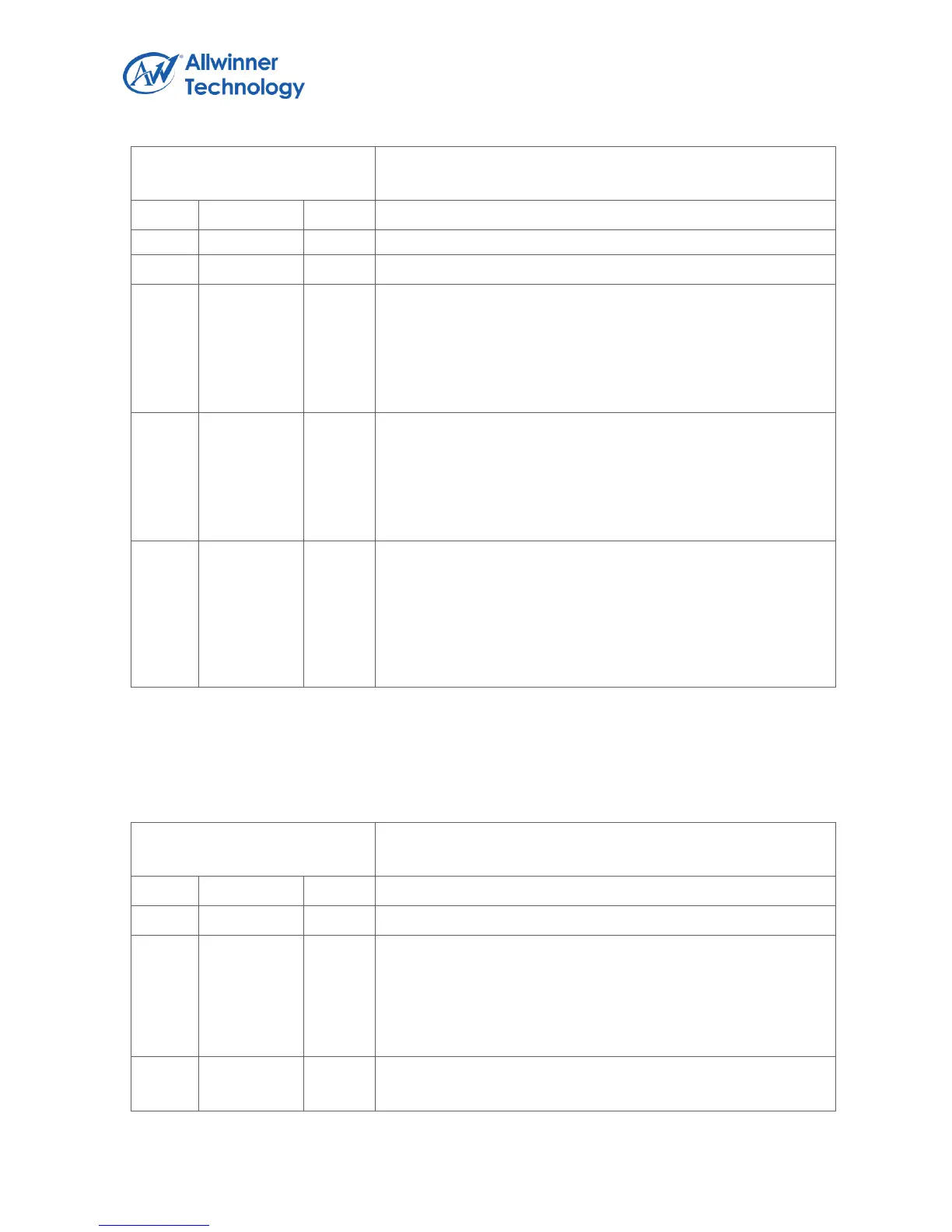

6.9.5.10. DIGITAL AUDIO CLOCK DIVIDE REGISTER

Register Name: DA_CLKD

Default Value: 0x0000_0000

MCLKO_EN

0: Disable MCLK Output

1: Enable MCLK Output

Notes: Whether in Slave or Master mode, when this bit is set to

1, MCLK should be output.

BCLKDIV

BCLK Divide Ratio from MCLK

Loading...

Loading...