A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 765 / 812

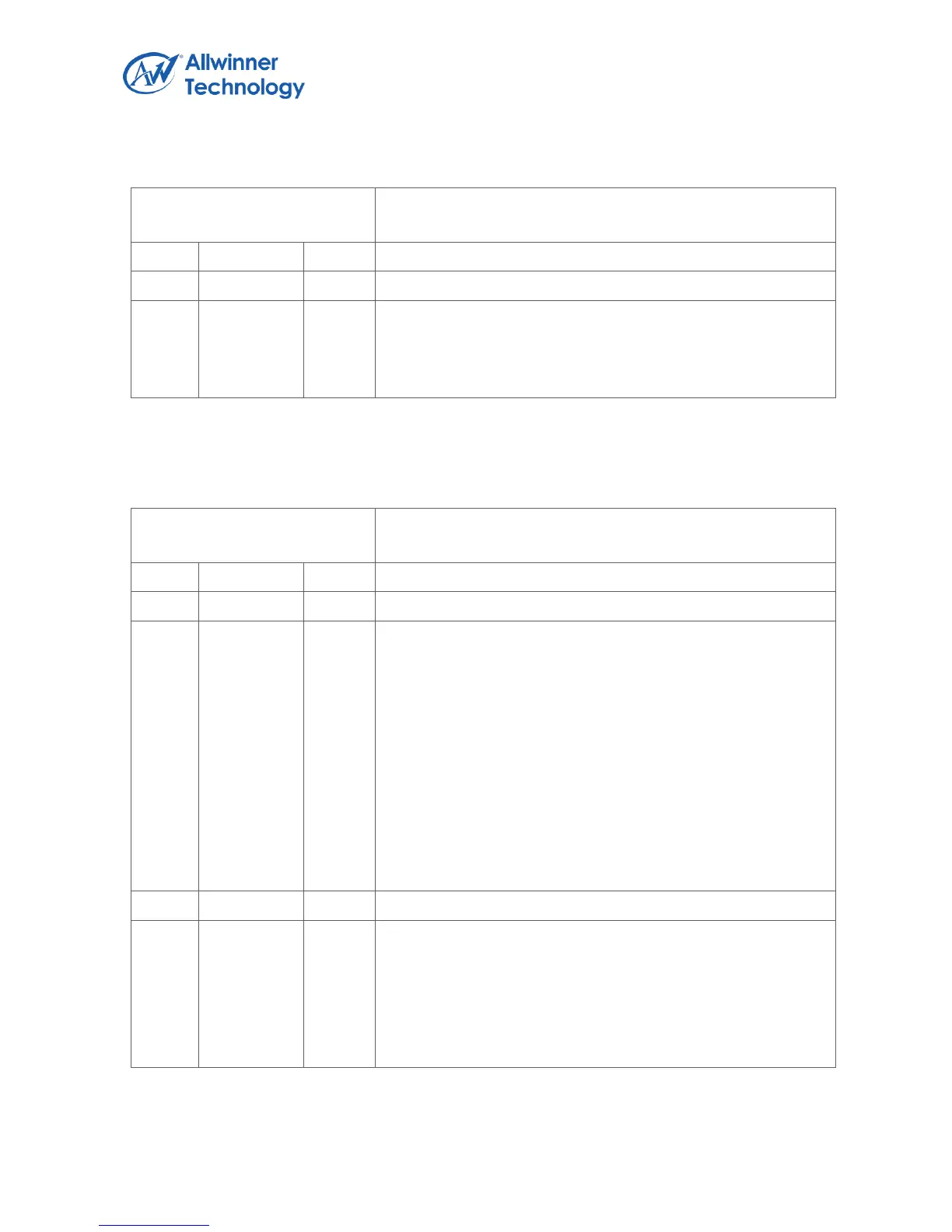

6.13.4.31. TSF CHANNEL BUFFER BASE ADDRESS REGISTER

Register Name: TSF_CBBAR

Default Value: 0x0000_0000

TSFBufBAddr

Data Buffer Base Address for Channel

It is 4-word (16Bytes) align address. The LSB four bits should

be zero.

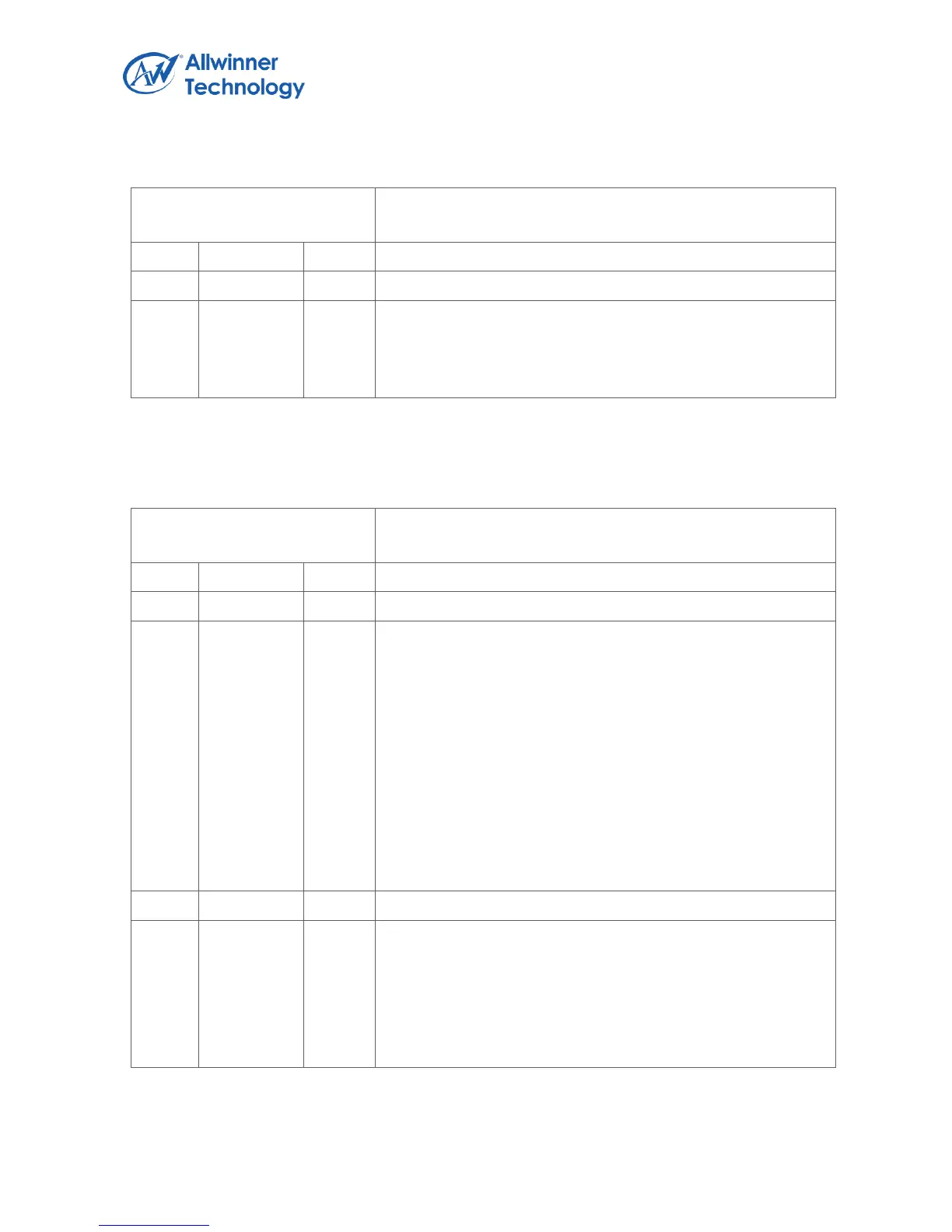

6.13.4.32. TSF CHANNEL BUFFER SIZE REGISTER

Register Name: TSF_CBSZR

Default Value: 0x0000_0000

CHDMAIntThd

DMA Interrupt Threshold for Channel

The unit is TS packet size. When received packet (has also

stored in DRAM) size is beyond (>=) threshold value, the

corresponding channel interrupt is generated to CPU. TSC

should count the new received packet again, when exceed the

specified threshold value, one new interrupt is generated

again.

0: 1/2 data buffer packet size

1: 1/4 data buffer packet size

2: 1/8 data buffer packet size

3: 1/16 data buffer packet size

CHBufPktSz

Data Buffer Packet Size for Channel

The exact buffer size of buffer is N+1 bytes.

The maximum buffer size is 2MB.

This size should be 4-word (16 Bytes) aligned. The LSB four

bits should be zero.

Loading...

Loading...