A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 772 / 812

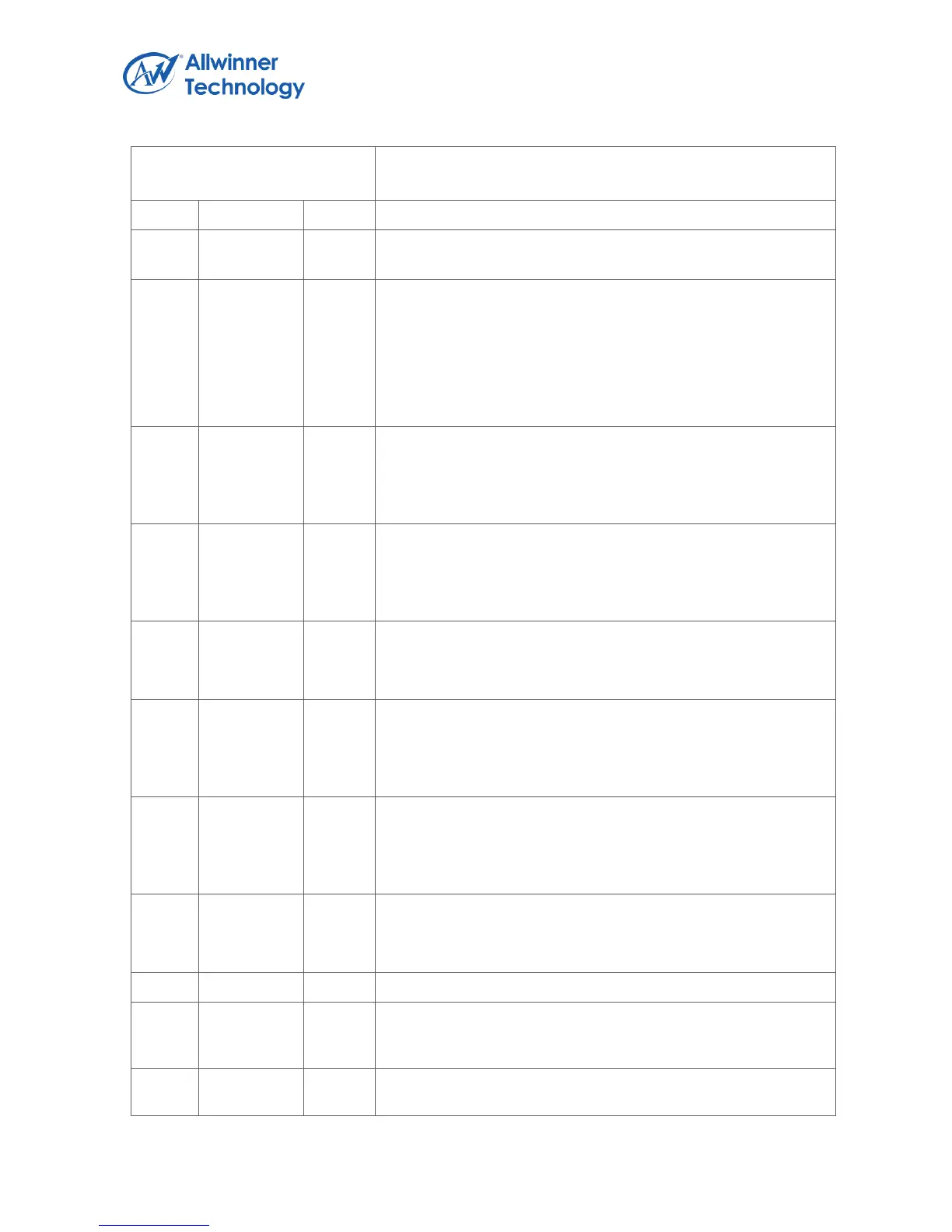

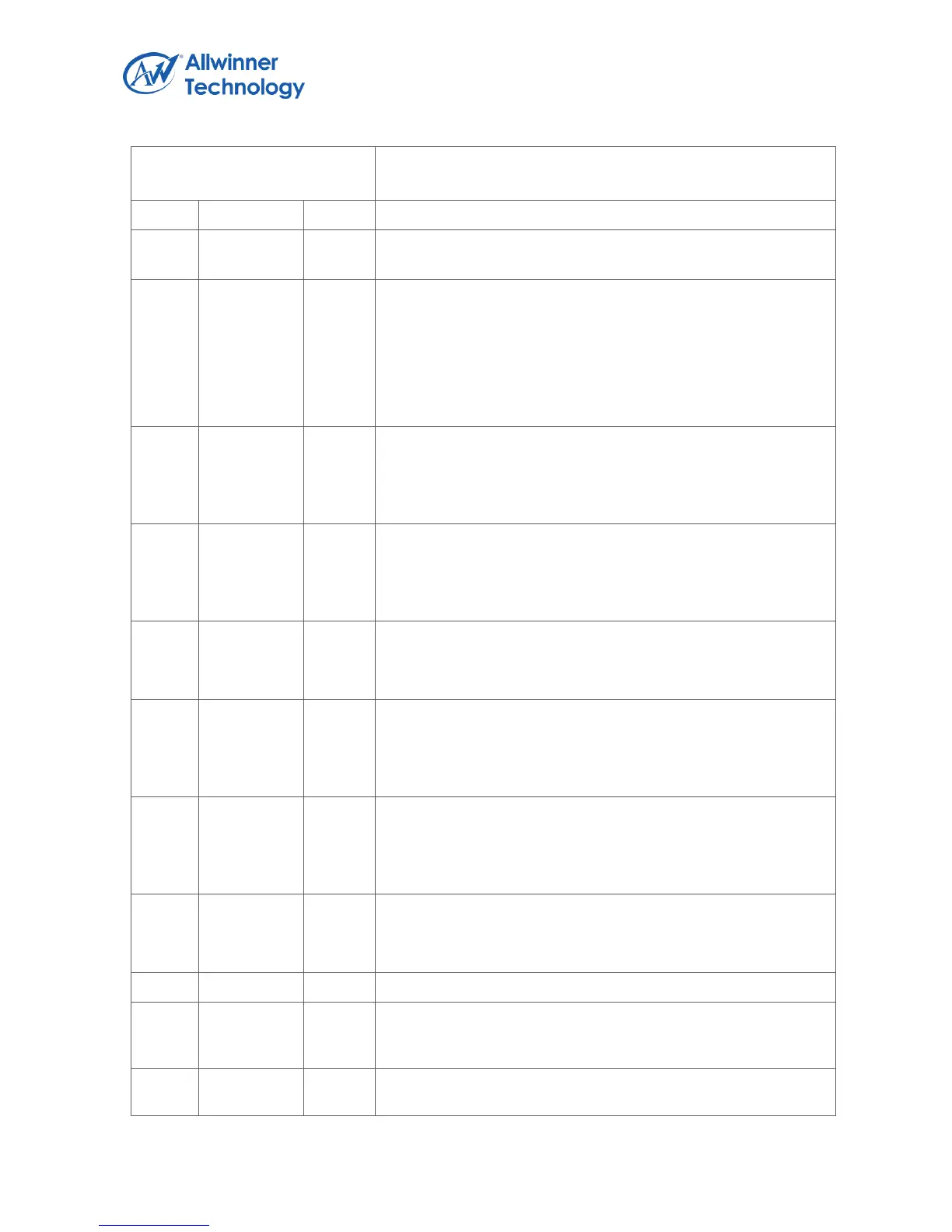

Register Name: SCR_CSR

Default Value: 0x00000000

0: Low Active

1: High Active

Protocol Selection (PTLSEL)

0x0 – T=0.

0x1 – T=1, no character repeating and no guard time is used

when T=1 protocol is selected.

0x2 – Reserved

0x3 – Reserved

ATRSTFLUSH

ATR Start Flush FIFO

When enabled, both FIFOs are flushed before the ATR is

started.

TSRXE

TS Receive Enable

When set to ‘1’, the TS character (the first ATR character) will

be store in RXFIFO during card session.

CLKSTPPOL

Clock Stop Polarity

The value of the scclk output during the clock stop state.

PECRXE

Parity Error Character Receive Enable

Enables storage of the characters received with wrong parity

in RX FIFO.

MSBF

MSB First

When high, inverse bit ordering convention (msb to lsb) is

used.

DATAPOL

Data Plorarity

When high, inverse level convention is used (A=’1’, Z=’0’).

DEACTDeactivation. Setting of this bit initializes the

deactivation sequence. When the deactivation is finished, the

DEACT bit is automatically cleared.

ACT

Activation. Setting of this bit initializes the activation sequence.

Loading...

Loading...