A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 773 / 812

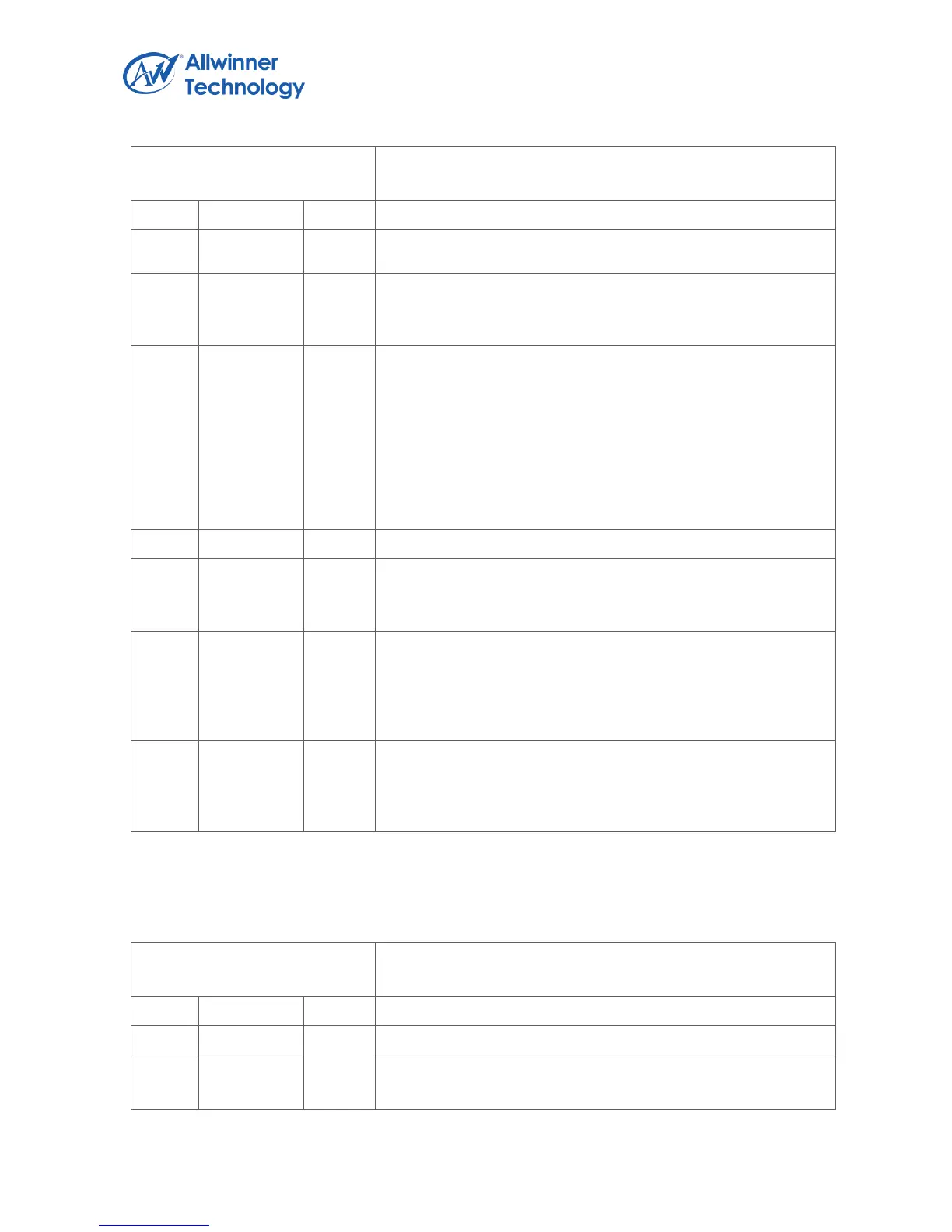

Register Name: SCR_CSR

Default Value: 0x00000000

When the activation is finished, the ACT bit is automatically

cleared.

WARMRST

Warm Reset Command. Writing ‘1’ to this bit initializes Warm

Reset of the Smart Card. This bit is always read as ‘0’.

CLKSTOP

Clock Stop. When this bit is asserted and the smart card I/O

line is in ‘Z’ state, the SCR core stops driving of the smart card

clock signal after the CLKSTOPDELAY time expires. The

smart card clock is restarted immediately after the CLKSTOP

signal is deasserted. New character transmission can be

started after CLKSTARTDELAY time. The expiration of both

times is signaled by the CLKSTOPRUN bit in the interrupt

registers.

GINTEN

Global Interrupt Enable. When high, IRQ output assertion is

enabled.

RXEN

Receiving Enable. When enabled the characters sent by the

Smart Card are received by the UART and stored in RX FIFO.

Receiving is internally disabled while a transmission is in

progress.

TXEN

Transmission Enable. When enabled the characters are read

from TX FIFO and transmitted through UART to the Smart

Card.

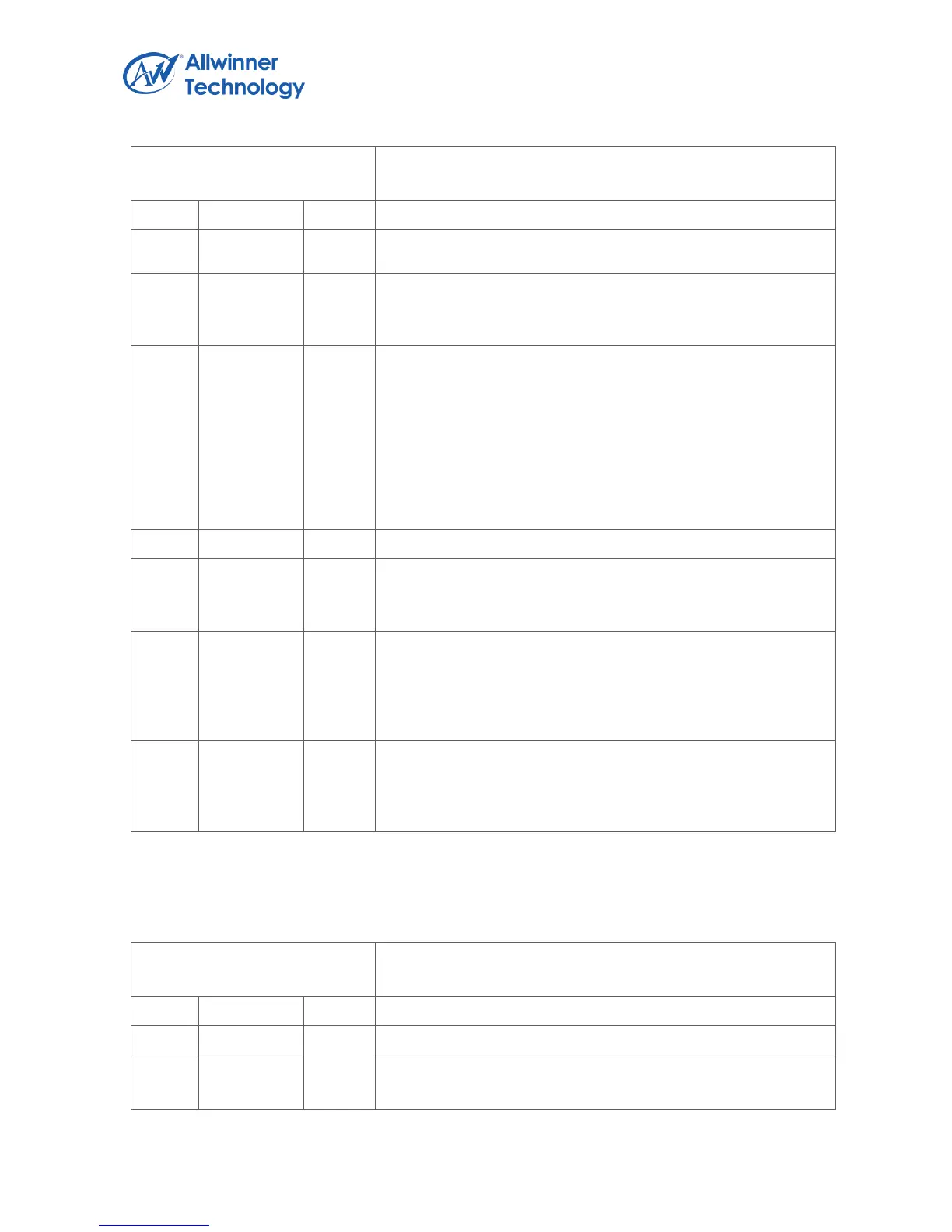

6.14.5.2. SMART CARD READER INTERRUPT ENABLE REGISTER

Register Name: SCR_INTEN

Default Value: 0x00000000

SCDEA

Smart Card Deactivation Interrupt Enable.

Loading...

Loading...