A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 775 / 812

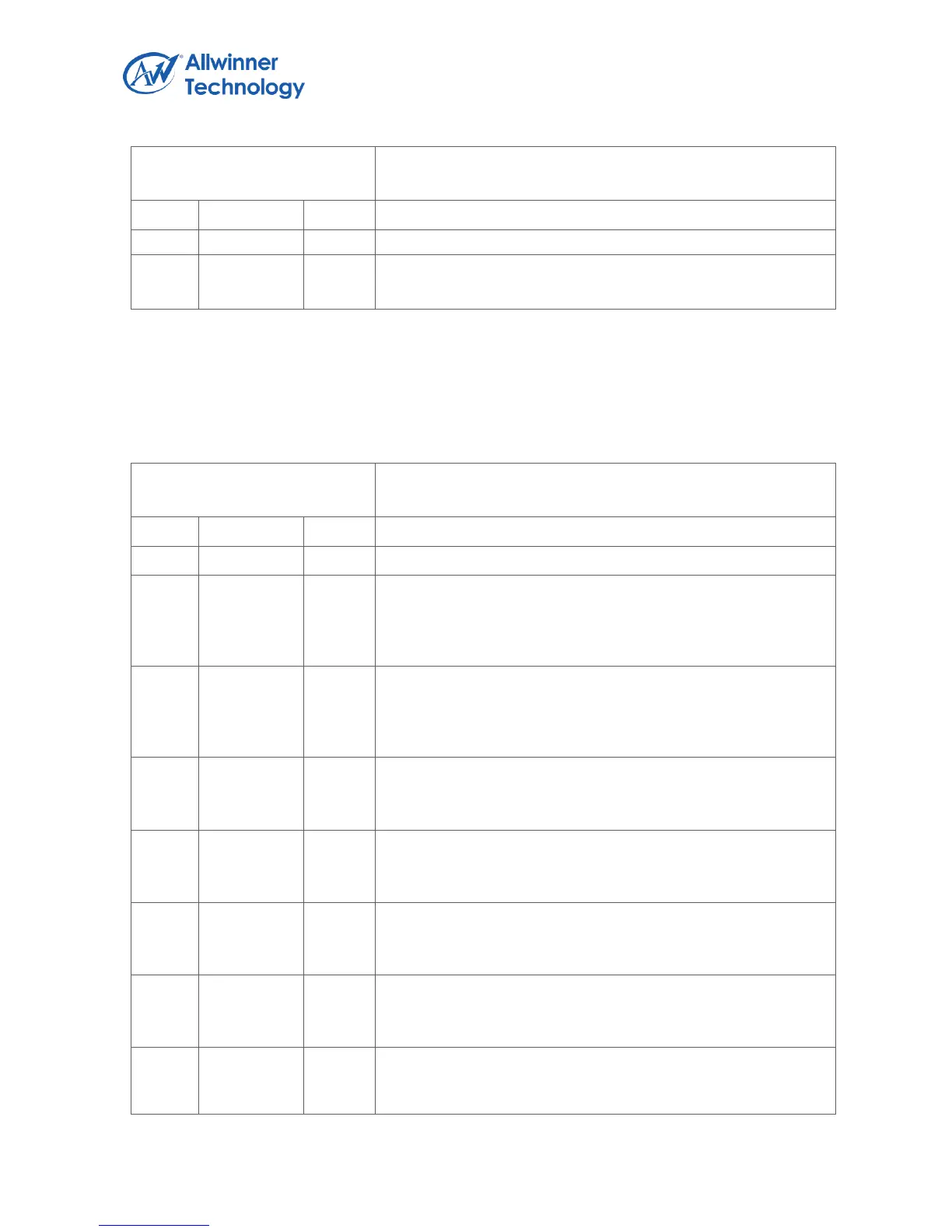

Register Name: SCR_INTEN

Default Value: 0x00000000

TX FIFO Empty Interrupt Enable.

TXFIFODONE

TX FIFO Done Interrupt Enable.

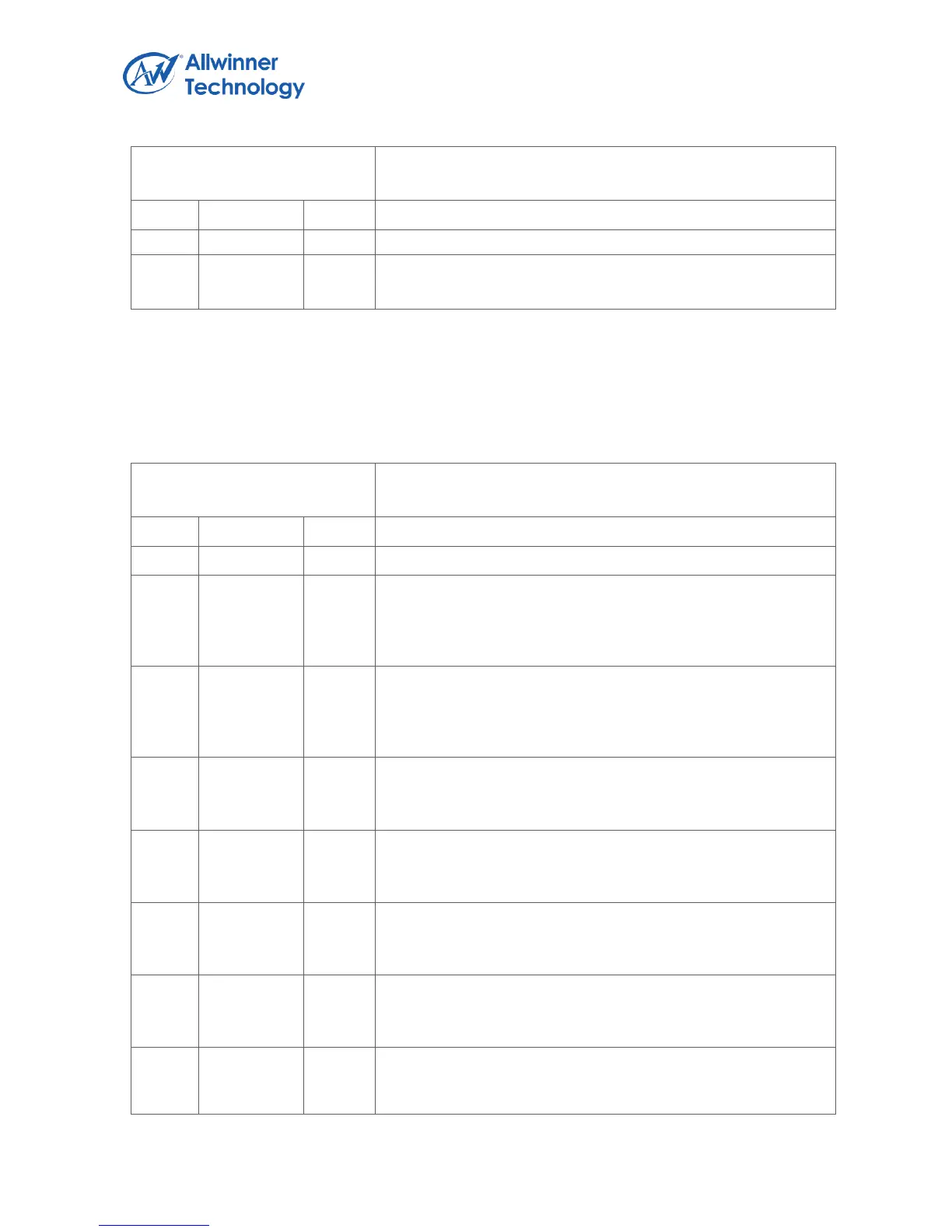

6.14.5.3. SMART CARD READER INTERRUPT STATUS REGISTER

This 16-bit register provides information about the state of each interrupt bit. You can clear the

register bits individually by writing ‘1’ to a bit you intend to clear.

Register Name: SCR_INTST

Default Value: 0x00000000

SCDEA

Smart Card Deactivation Interrupt. When enabled, this

interrupt is asserted after the Smart Card deactivation

sequence is complete.

SCACT

Smart Card Activation Interrupt. When enabled, this interrupt is

asserted after the Smart Card activation sequence is

complete.

SCINS

Smart Card Inserted Interrupt. When enabled, this interrupt is

asserted after the smart card insertion.

SCREM

Smart Card Removed Interrupt. When enabled, this interrupt is

asserted after the smart card removal.

ATRDONE

ATR Done Interrupt. When enabled, this interrupt is asserted

after the ATR sequence is successfully completed.

ATRFAIL

ATR Fail Interrupt. When enabled, this interrupt is asserted if

the ATR sequence fails.

C2CFULL

Two Consecutive Characters Limit Interrupt. When enabled,

this interrupt is asserted if the time between two consecutive

Loading...

Loading...