A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 776 / 812

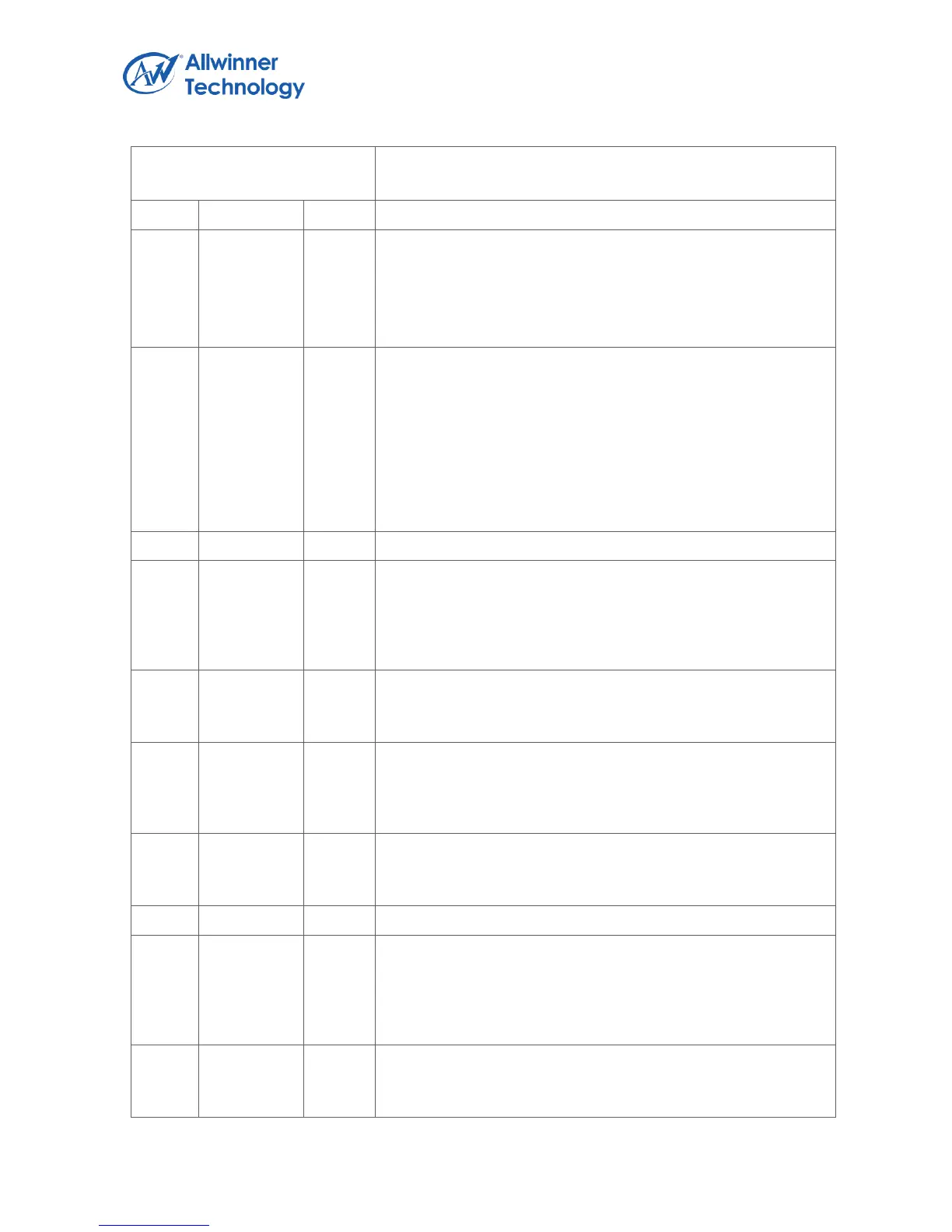

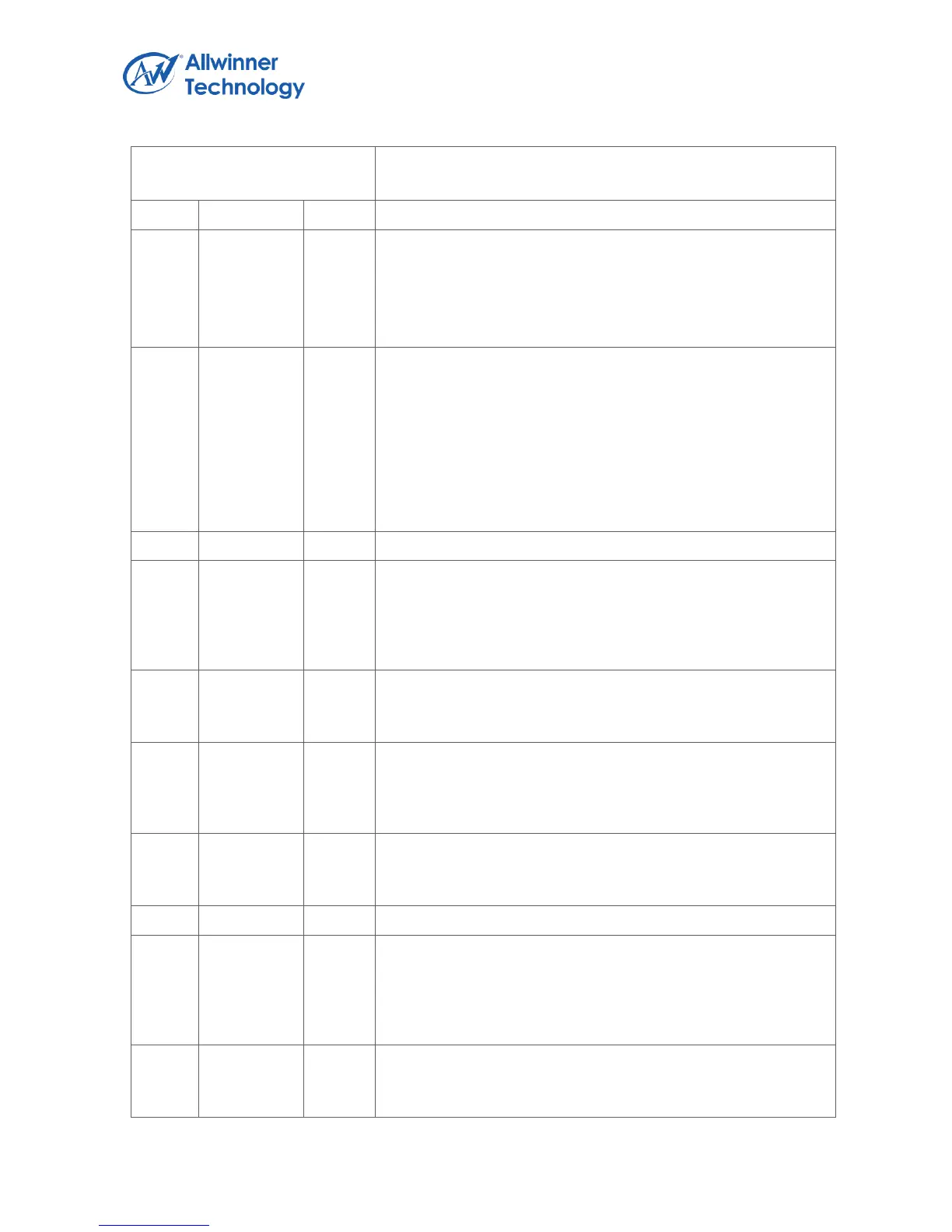

Register Name: SCR_INTST

Default Value: 0x00000000

characters, transmitted between the Smart Card and the

Reader in both directions, is equal the Two Characters Delay

Limit described below. The C2CFULL interrupt is internally

enabled from the ATR start to the deactivation or ATR restart

initialization. It is recommended to use this counter to detect

unresponsive Smart Cards.

CLKSTOPRUN

Smart Card Clock Stop/Run Interrupt. When enabled, this

interrupt is asserted in two cases:

When the smart card clock is stopped.

When the new character can be started after the clock restart.

To distinguish between the two interrupt cases, we

recommend reading the CLKSTOP bit in SCR_CTRL1

register.

RXPERR

RX Parity Error Interrupt. When enabled, this interrupt is

asserted after the character with wrong parity was received

when the number of repeated receptions exceeds RXREPEAT

value or T=1 protocol is used.

RXDONE

RX Done Interrupt. When enabled, this interrupt is asserted

after a character was received from the Smart Card.

RXFIFOTHD

RX FIFO Threshold Interrupt. When enabled, this interrupt is

asserted if the number of bytes in RX FIFO is equal or exceeds

the RX FIFO threshold.

RXFIFOFULL

RX FIFO Full Interrupt. When enabled, this interrupt is

asserted if the RX FIFO is filled up.

TXPERR

TX Parity Error Interrupt. When enabled, this interrupt is

asserted if the Smart Card signals wrong character parity

during the guard time after the character transmission was

repeated TXREPEAT times or T=1 protocol is used.

TXDONE

TX Done Interrupt. When enabled, this interrupt is asserted

after one character was transmitted to the smart card.

Loading...

Loading...