A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 792 / 812

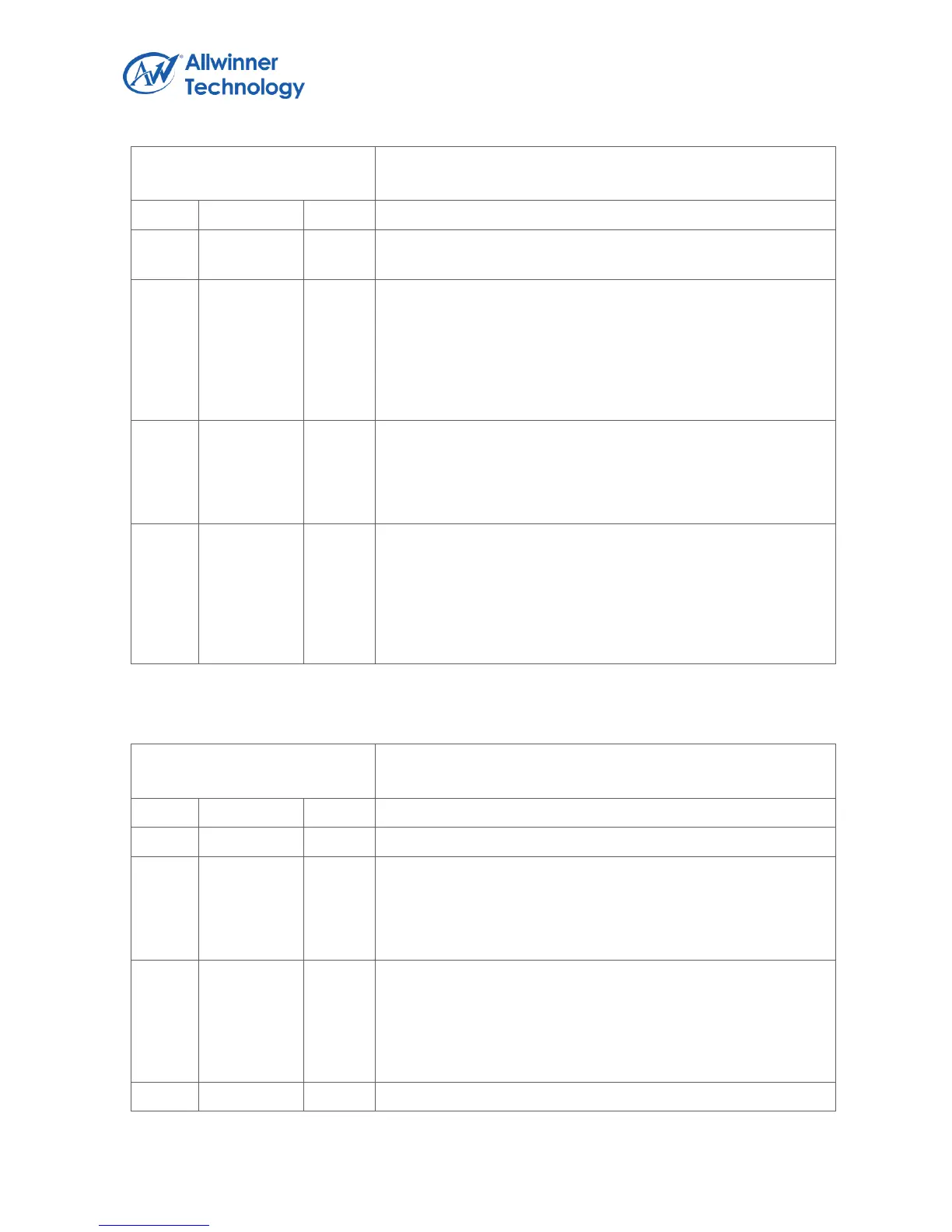

Register Name:

CAN_STA_REG

Default Value: 0x0000_003C

completed

0 - The last requested transmission has not been completed

TX_RDY

Tx Buffer Ready

1 – Tx buffer ready. Transmit buffer is released. The CPU may

write a message to transmit buffer

0 – Tx buffer not ready. Transmit buffer is locked. The CPU

cannot access the tx buffer.

DATA_OR

Data overrun

1 – data buffer overrun

0 – data buffer not overrun

RX_RDY

Rx Buffer Ready

1 – Rx buffer is not empty. One or more message are available

to be read from Rx buffer

0 – Rx buffer is empty. No message currently available to be

read

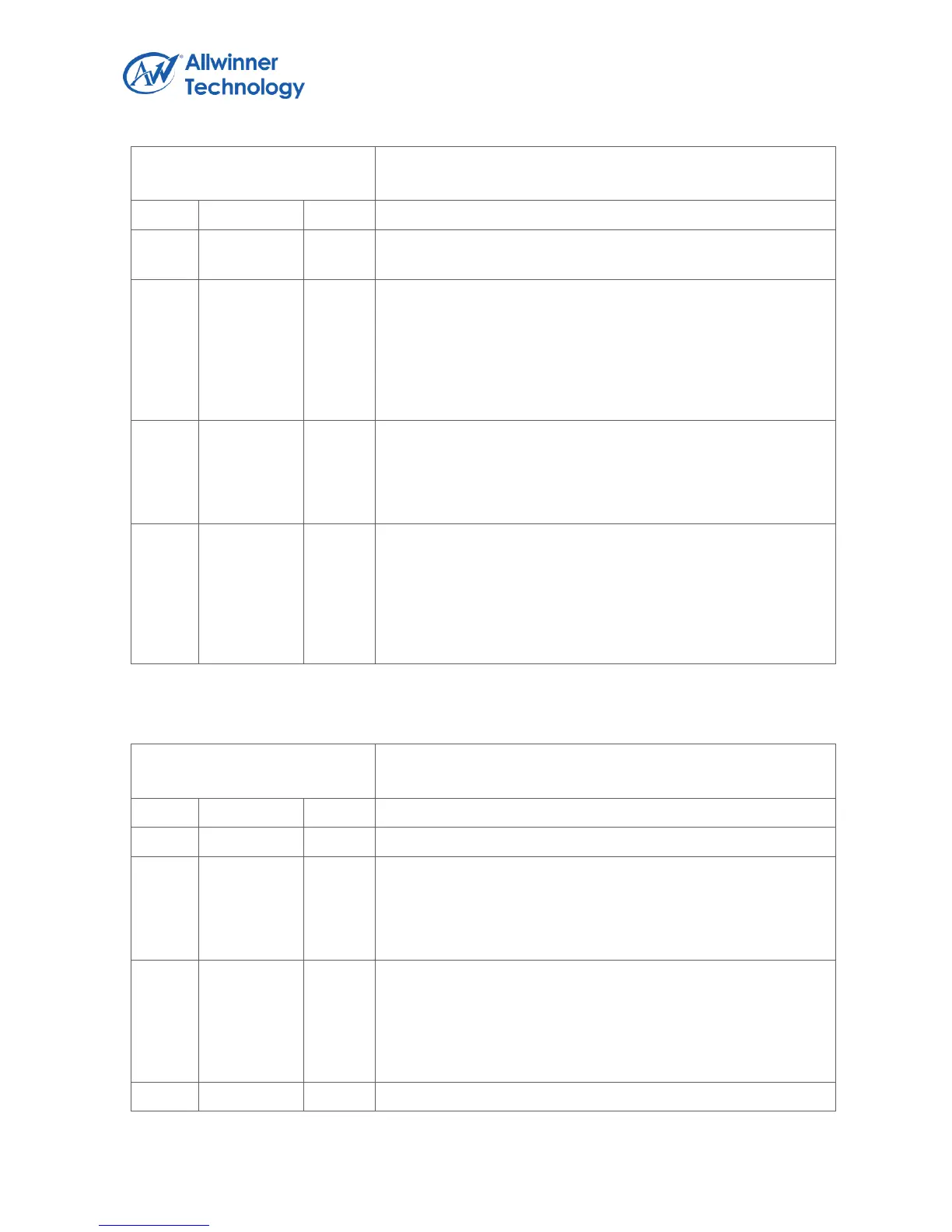

6.16.5.4. CAN INTERRUPT REGISTER

Register Name:

CAN_INT_REG

Default Value: 0x0000_0000

BERR

Bus Error Interrupt

Set when the controller detects an bit error on the CAN bus

This is a wirte-1-to-clear bit.

ARB_LOST

Arbitration Lost Interrupt

Set when the controller loses arbitration and becomes a

receiver

This is a wirte-1-to-clear bit.

Loading...

Loading...