A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 793 / 812

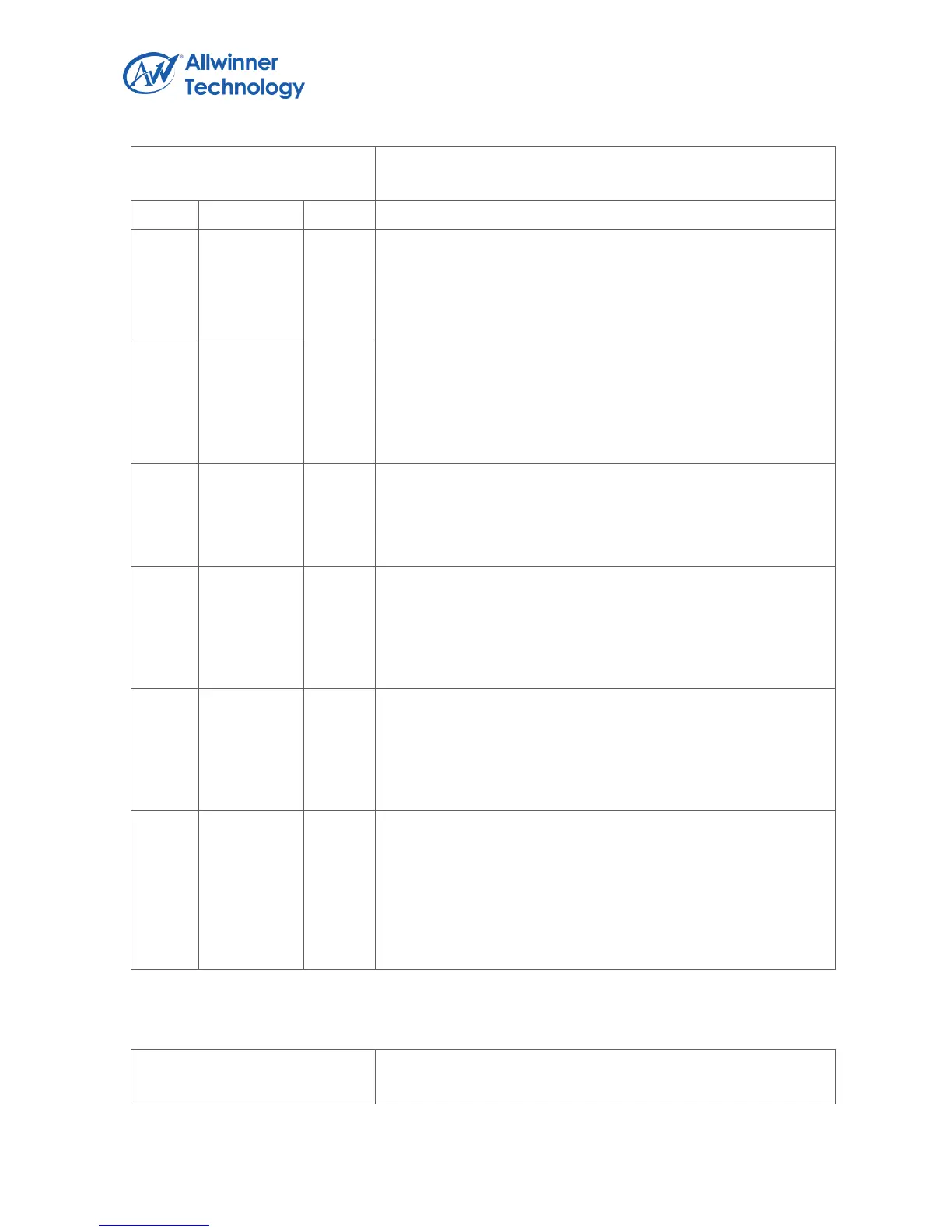

Register Name:

CAN_INT_REG

Default Value: 0x0000_0000

Error Passive Interrupt

Set when the controller re-enters error active state after being

in error passive state or when at least one error counter

exceeds the protocol-defined level of 127

This is a wirte-1-to-clear bit.

WAKEUP

Wake-Up Interrupt

Set when bus activity is detected while the CAN controller is

sleeping

This is a read-to-clear bit.

DATA_OR

Data Overrun Interrupt

Set on a ‘0-to-1’ transition of the Data Overrun Status bit

This is a wirte-1-to-clear bit.

ERR

Error Warning Interrupt

Set on every change (set or clear) of either the Bus Status or

Error Status bits (SR.7,SR.6)

This is a wirte-1-to-clear bit.

TX_FLAG

Transmit Interrupt Flag

Set whenever the Transmit Buffer Status (SR.2) changes from

‘0-to-1’ (released)

This is a wirte-1-to-clear bit.

RX_FLAG

Receive Interrupt Flag

Set whenever the Receive Buffer contains one or more

messages. Cleared when the release Receive Buffer

command (CMR. 2) is issued, provided there is no further data

to read in the Receive Buffer.

This is a wirte-1-to-clear bit.

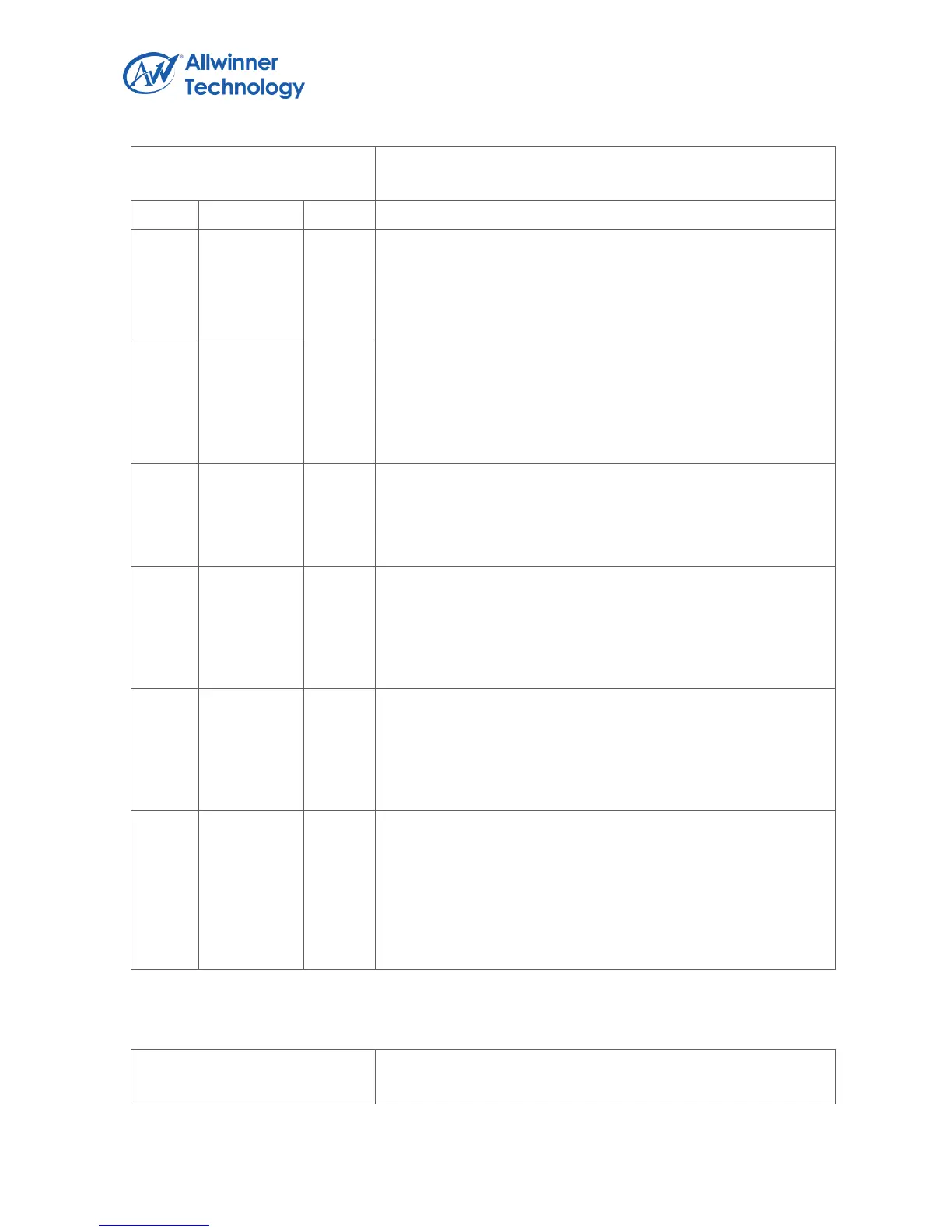

6.16.5.5. CAN INTERRUPT ENABLE REGISTER

Register Name:

CAN_INTE_REG

Default Value: 0x0000_0000

Loading...

Loading...