Chapter 8

8-bit Timer

Control Registers VIII - 19

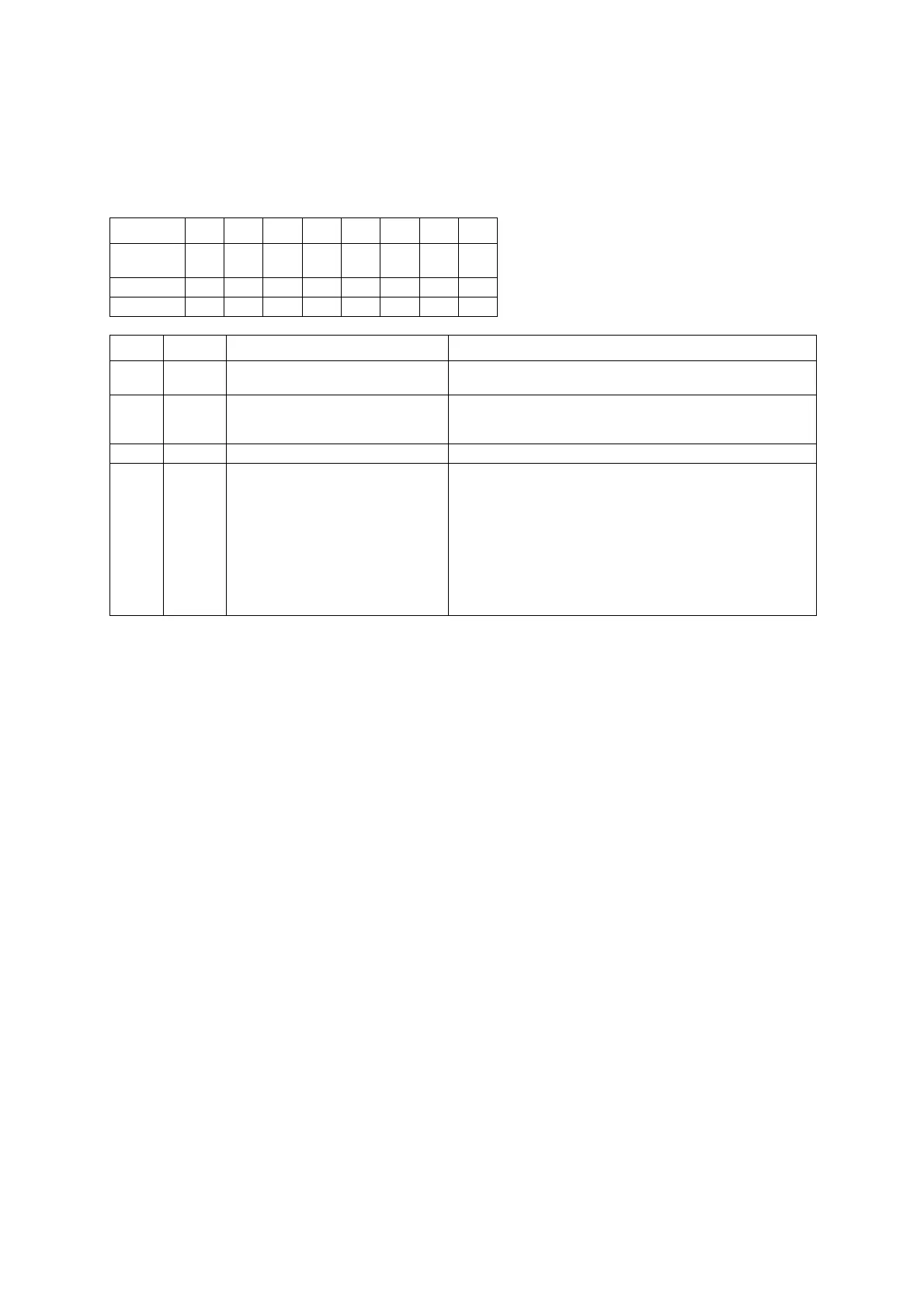

■ Timer 1 Mode Register (TM1MD: 0x0000A181) [8-bit Access Register]

bp 76543210

Flag TM1

CNE

TM1

LDE

---TM1

CK2

TM1

CK1

TM1

CK0

At reset 00000000

Access R/W R/W R R R R/W R/W R/W

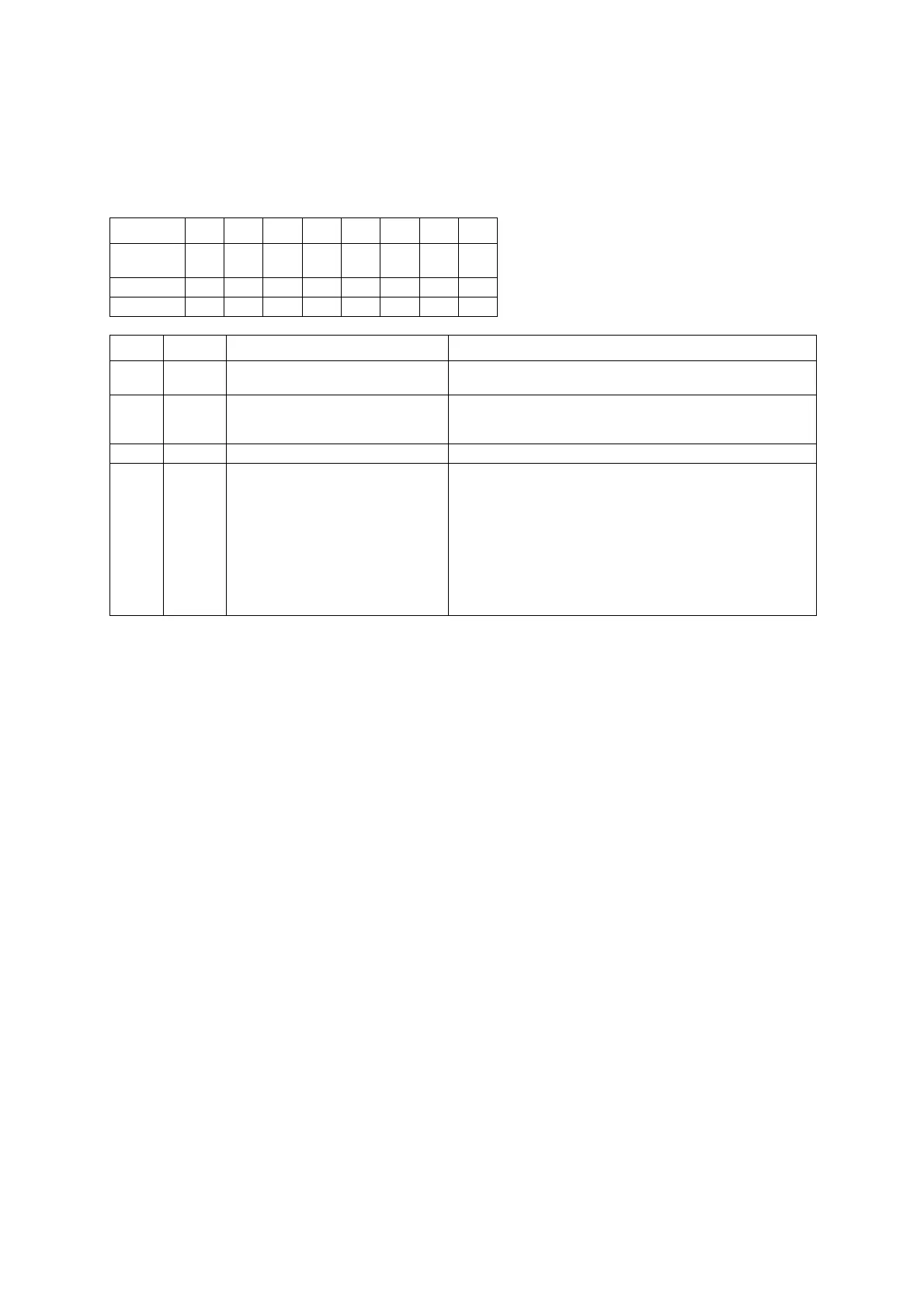

bp Flag Description Set condition

7TM1CNE

Timer operation enable 0: Operation disabled

1: Operation enabled

6TM1LDE

Timer initialization 0: Normal operation

1: Initialization

TM1BR value is loaded into TM1BC. Timer output 1 is set to “L” level.

5-3 - - -

2-0

TM1CK2

TM1CK1

TM1CK0

Count clock source selection 000: IOCLK

001: IOCLK/8

010: IOCLK/32

011: Cascading with timer 0

100: Timer 0 underflow

101: Setting prohibited

110: Timer 2 underflow

111: TM1IO pin input (rising edge)

When 1/8 IOCLK and 1/32 IOCLK are used, the prescaler control reg-

ister (TM03PSC) should be set.

Loading...

Loading...