Chapter 9

16-bit Timer

Control registers IX - 15

■ Timer 8 Compare/Capture A Register (TM8CA: 0x0000A208) [16-bit Access Register]

This is a register which has compare operation and capture operation. For the appropriate use of both operations,

this register is set by the TMAM1-0 flag of the timer compare capture A(B) register. For compare operation,

select the compare capture register to be used as double buffer or single buffer. For capture operation, set the both-

edge or one-edge of an input pin to the capture timing.

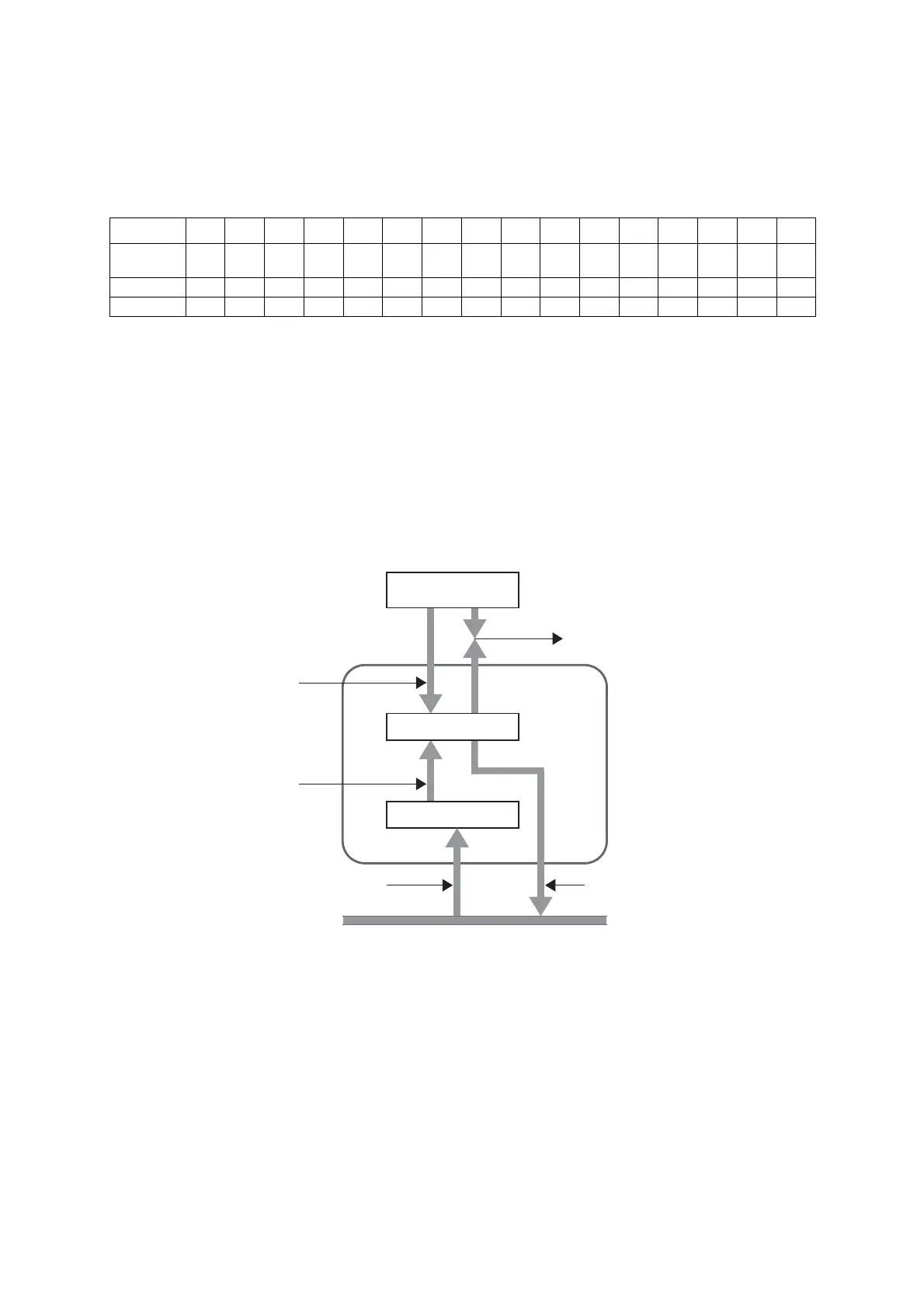

1. When the compare/capture register is set to compare operation

The interrupt request (TMAIRQ, TMBIRQ) is generated at the time when the binary counter (TMnBC) and

the compare capture register (TMnCA, TMnCB) match. Figure: 9.2.1 shows the block diagram of the compare

capture/register.

Figure:9.2.1 Block Diagram of Compare/Capture Register

When the compare capture register is set to the double buffer, the value of the TMnCA (TMnCB) is retained in

the compare register buffer once; so, when the it is read again after writing to the TMnCA (TMnCB), the pre-

vious value may be returned. Table: 9.2.3 shows the timing when the compare/capture register is updated at

double buffer.

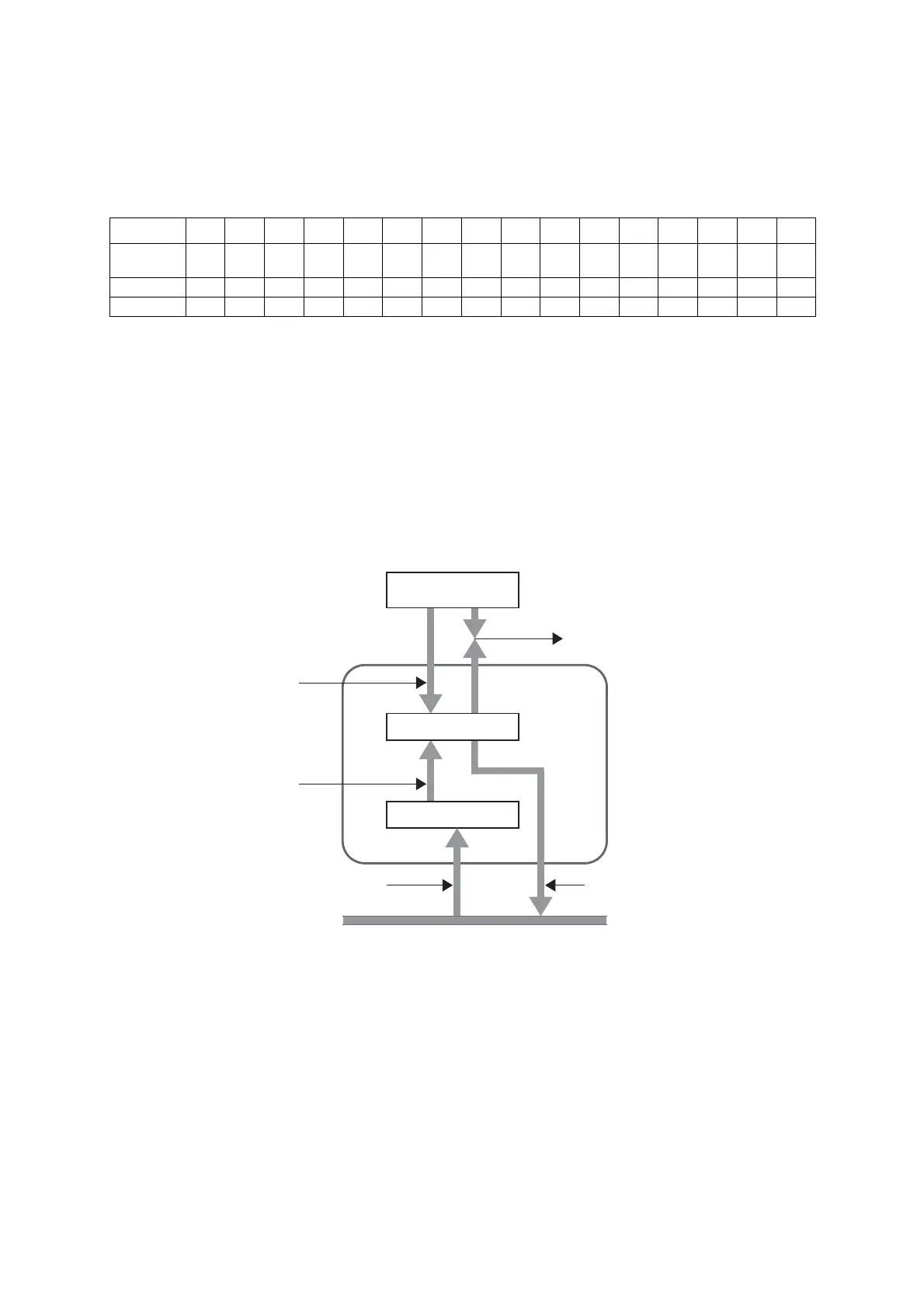

bp 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Flag TM

CA15

TM

CA14

TM

CA13

TM

CA12

TM

CA11

TM

CA10

TM

CA9

TM

CA8

TM

CA7

TM

CA6

TM

CA5

TM

CA4

TM

CA3

TM

CA2

TM

CA1

TM

CA0

At reset 0000000000000000

Access R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Compare/capture register

Timer compare/capture A and B register

Compare register buffer

Data bus

Register write

Register read

Timing of load to

compare register

Capture timing

Compare/capture A(B) register

TMnCA (TMnCB)

Match interrupt reques

TMnBC

binary counter

Loading...

Loading...