Chapter 9

16-bit Timer

IX - 16 Control registers

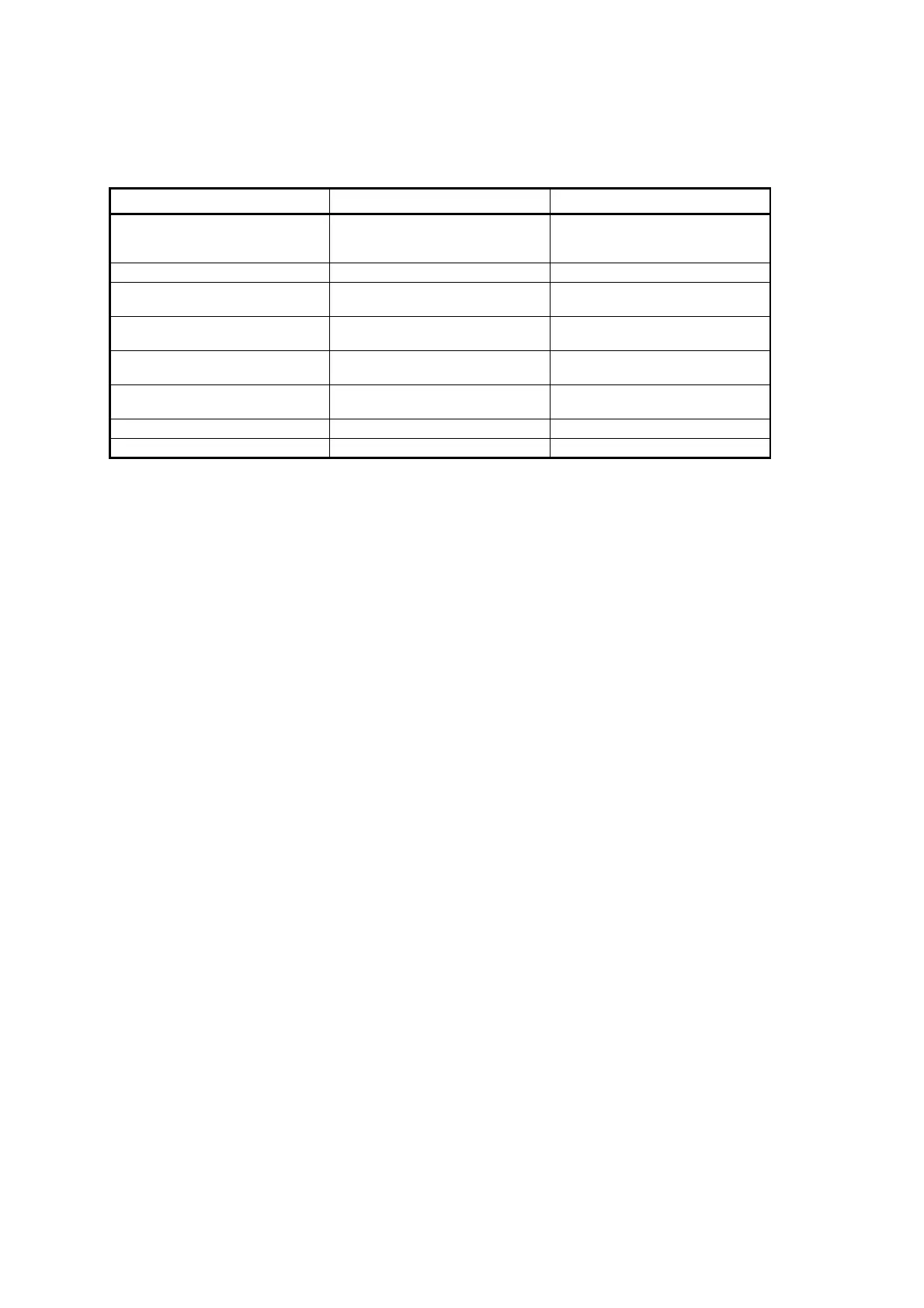

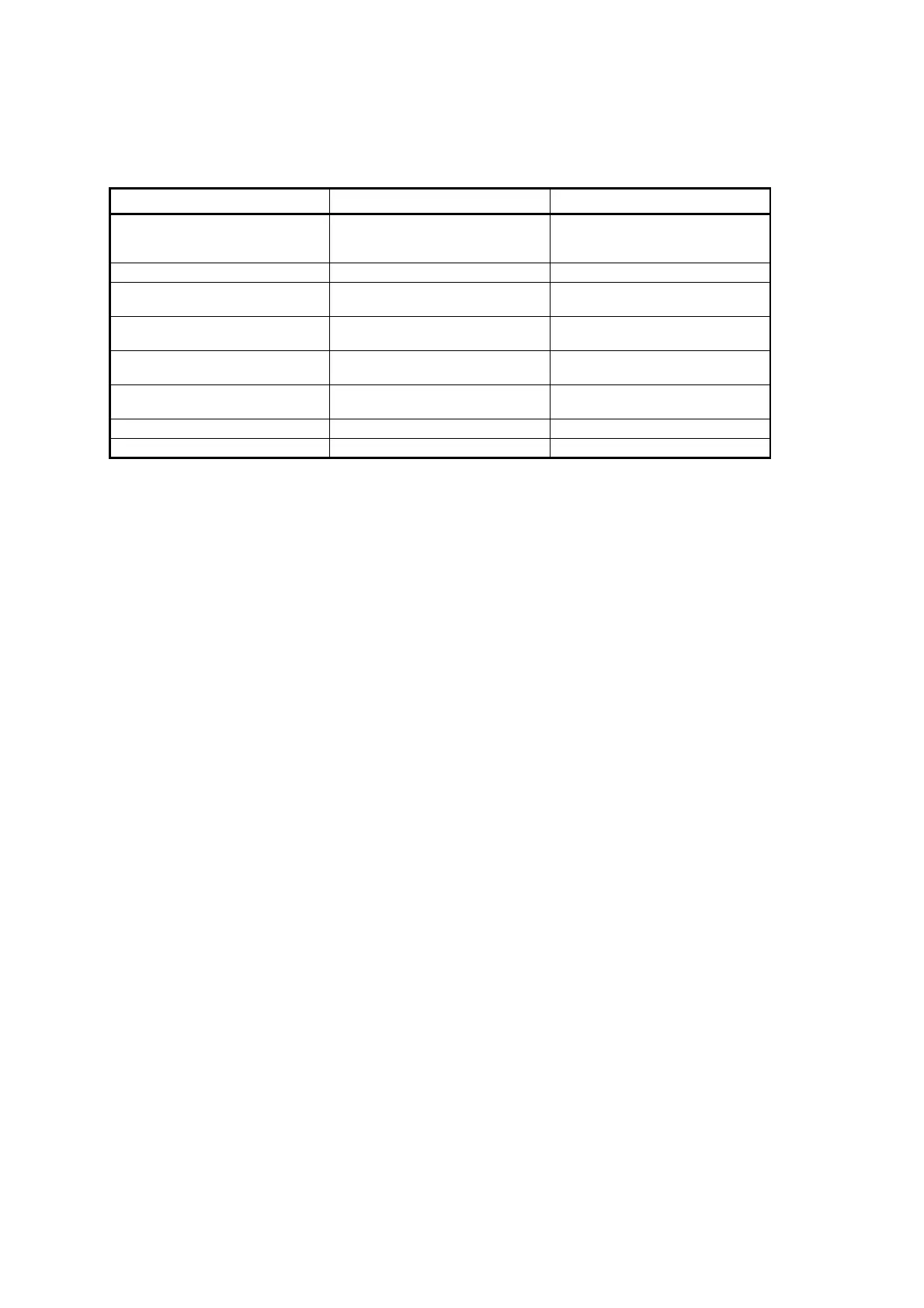

Table:9.2.3 Updated Timing of Compare/Capture Register (At Double Buffer)

TMnCBUFF: compare register buffer

2. When the compare/capture register is set to capture operation

The value of the TMnBC is captured into TMnCA (TMnCB) by inputting the edge selected to the TMAIN

(TMBIN) pin; and, the interrupt request (TMAIRQ, TMBIRQ) is generated.

TMLCE flag (TMnMD)=0 TMLCE flag (TMnMD)=1

When initializing a timer (when the

TMLDE flag of the TMnMD register is set

to “1”)

TMnCA←TMnCBUFF *1

TMnCB←TMnCBUFF

TMnCA←TMnCBUFF

TMnCB←TMnCBUFF

Count clock up (down) - -

TMnBC overflow TMnCA←TMnCBUFF

TMnCB←TMnCBUFF

-

TMnBC underflow TMnCA←TMnCBUFF

TMnCB←TMnCBUFF

-

Counting up (down) when the TMnBC

and the TMnCA match

-TMnCA←TMnCBUFF

TMnCB←TMnCBUFF *2

Counting up (down) when the TMnBC

and the TMnCB match

--

At the TMnCA capture - TMnBC←TMnCBUFF *3

At the TMnCB capture - -

*1 TMnCBUFF: compare register buffer

*2 When the TMnCA is set to the compare register

*3 When the TMnCA is set to the capture register

Loading...

Loading...