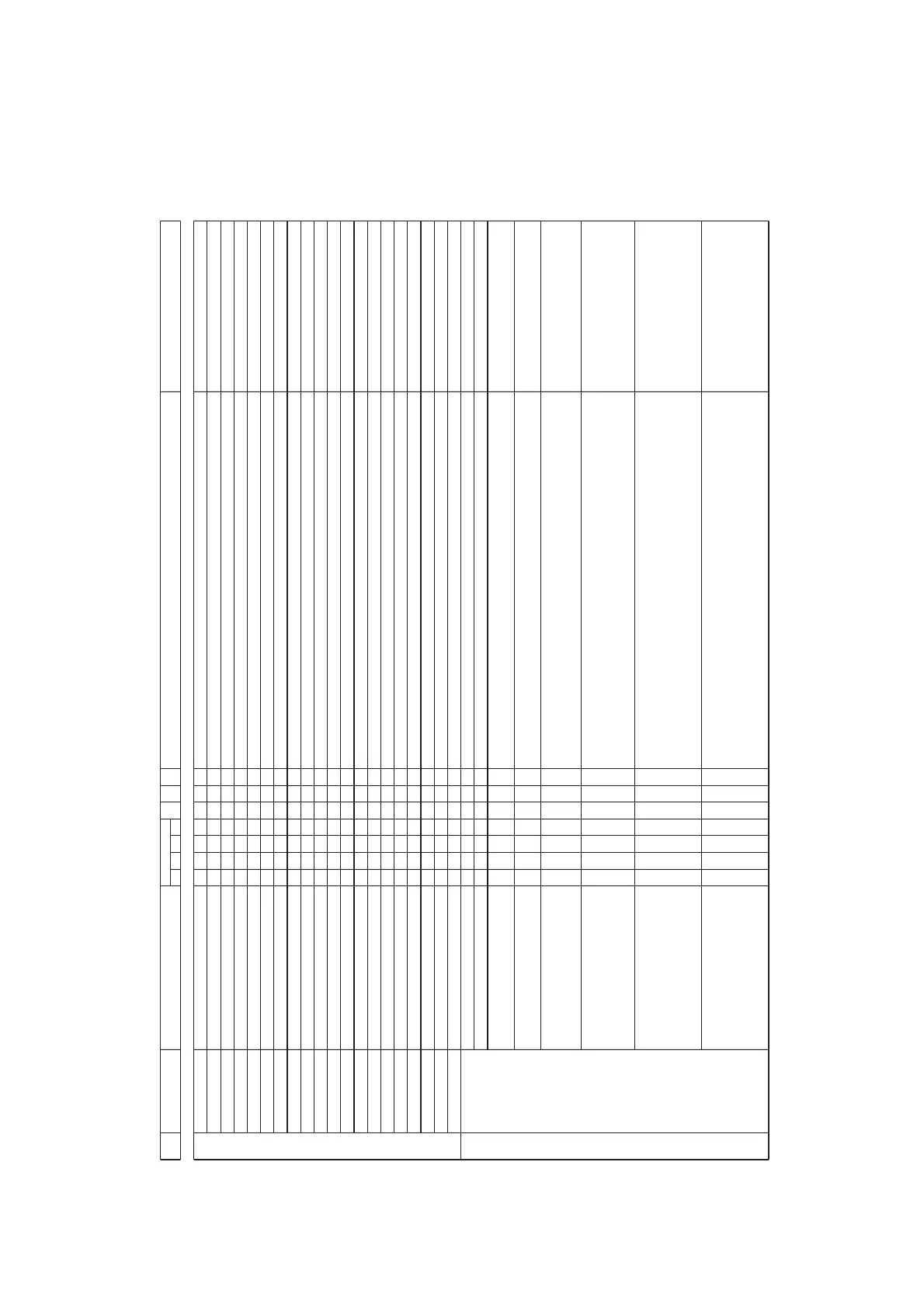

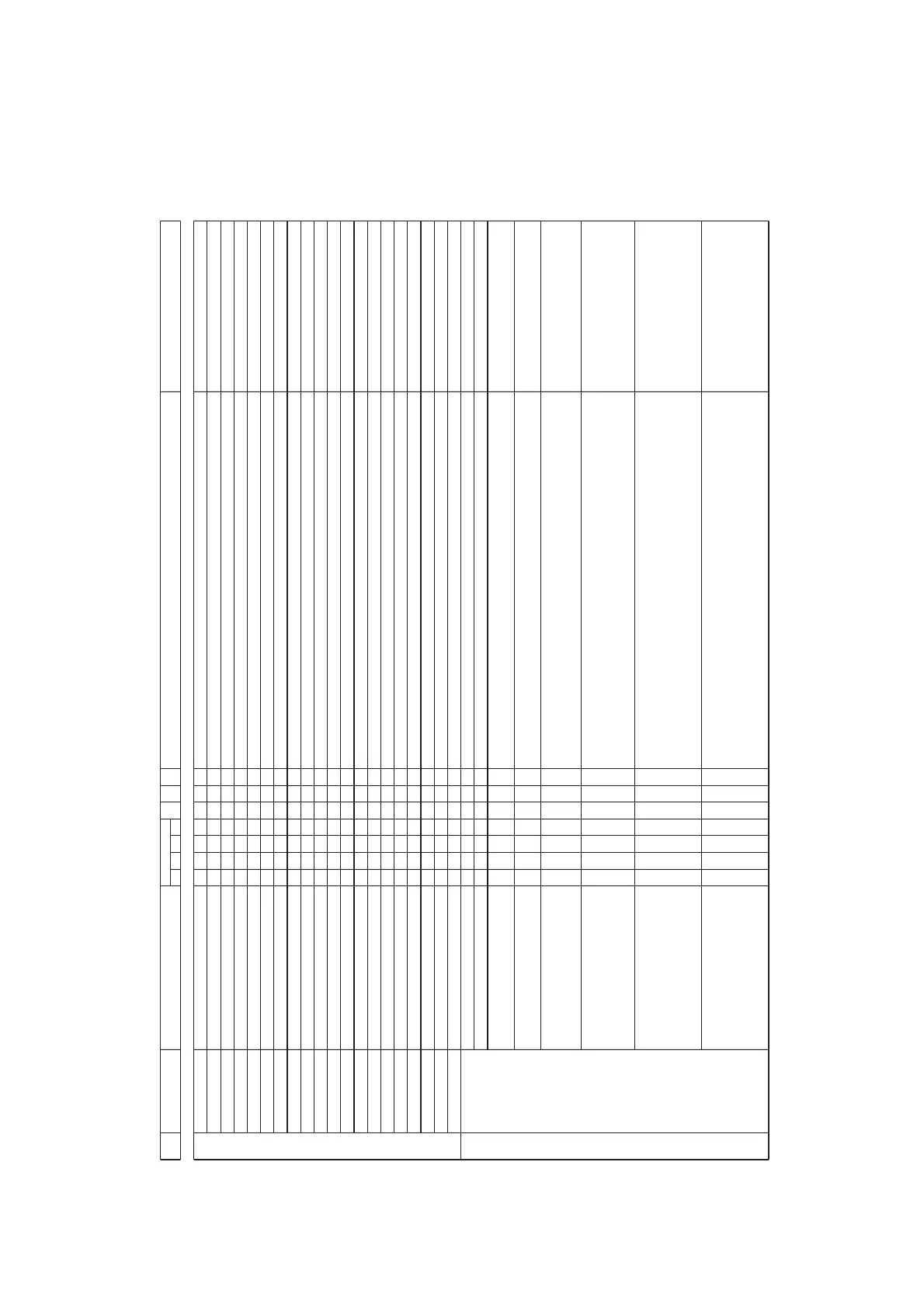

Chapter 16

Appendix

XVI - 10 Instruction Set

MOVH (Am),Dn

MOVH (d8,Am),Dn

MOVH (d16,Am),Dn

MOVH (d32,Am),Dn

MOVH (d8,SP),Dn

MOVH (d16,SP),Dn

MOVH (d32,SP),Dn

MOVH (Di,Am),Dn

MOVH (abs16),Dn

MOVH (abs32),Dn

MOVH Dm,(An)

MOVH Dm,(d8,An)

MOVH Dm,(d16,An)

MOVH Dm,(d32,An)

MOVH Dm,(d8,SP)

MOVH Dm,(d16,SP)

MOVH Dm,(d32,SP)

MOVH Dm,(Di,An)

MOVH Dm,(abs16)

MOVH Dm,(abs32)

MOVM (SP),[reg1,.,regn]

mem16(Am)(sign_ext) → Dn

mem16(d8(sign_ext)+Am)(sign_ext) → Dn

mem16(d16(sign_ext)+Am)(sign_ext) → Dn

mem16(d32+Am)(sign_ext) → Dn

mem16(d8(zero_ext)+SP)(sign_ext) → Dn

mem16(d16(zero_ext)+SP)(sign_ext) → Dn

mem16(d32+SP)(sign_ext) → Dn

mem16(Di+Am)(sign_ext) → Dn

mem16(abs16(zero_ext))(sign_ext) → Dn

mem16(abs32)(sign_ext) → Dn

Dm → mem16(An)

Dm → mem16(d8(sign_ext)+An)

Dm → mem16(d16(sign_ext)+An)

Dm → mem16(d32+An)

Dm → mem16(d8(zero_ext)+SP)

Dm → mem16(d16(zero_ext)+SP)

Dm → mem16(d32+SP)

Dm → mem16(Di+An)

Dm → mem16(abs16(zero_ext))

Dm → mem16(abs32)

PC+2 → PC

mem32(SP) → reg,SP+4 → SP

mem32(SP+4) → reg1,mem32(SP) → reg2,

SP+8 → SP

mem32(SP+8) → reg1,mem32(SP+4) → reg2,

mem32(SP) → reg3,SP+12 → SP

mem32(SP+12) → D2,mem32(SP+8) → D3,

mem32(SP+4) → A2,mem32(SP) → A3,

SP+16 → SP

mem32(SP+28) → D0,mem32(SP+24) → D1,

mem32(SP+20) → A0,mem32(SP+16) → A1,

mem32(SP+12) → MDR,mem32(SP+8) → LIR,

mem32(SP+4) → LAR,SP+32 → SP

mem32(SP+32) → reg,mem32(SP+28) → D0,

mem32(SP+24) →D1,mem32(SP+20) →A0,

mem32(SP+16) →A1,mem32(SP+12) →MDR,

mem32(SP+8) →LIR,mem32(SP+4) →LAR,

SP+36 →SP

mem32(SP+36)→reg1, mem32(SP+32)→reg2,

mem32(SP+28)→D0,mem32(SP+24)→D1,

mem32(SP+20)→A0,mem32(SP+16)→A1,

mem32(SP+12)→MDR,mem32(SP+8)→LIR,

mem32(SP+4)→LAR,SP+40 →SP

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

3

4

5

7

4

5

7

3

4

7

2

3

4

6

3

4

6

2

3

6

2

2

2

2

2

2

2

2

2

2

2

3

2

2

3

2

2

3

1

1

1

2

1

1

2

2

1

2

1

2

3

4

5

8

9

10

S1

1

1100

2

1110

3

<regs

4

....>

56

Group

Mnemonic

Operation

Machine Code

Notes

Flag

Code

Size

Cycle

For

-mat

MN1030/MN103S SERIES INSTRUCTION SET

789

10

11

12

13 14

VF

CF NF

ZF

MOVH

MOVM

registers specified with regs = 0

registers specified with regs = 1

registers specified with regs = 2(*1)

registers specified with regs = 3(*1)

registers specified with regs = =4(*1)

registers specified with regs = 7

registers specified with regs = 8

registers specified with regs = 9(*1)

*1: registers specified with regn are returned in the order; D2, D3, A2 and A3 no matter when the assembler srites these

registers. Skip the registers which is not specified.

Loading...

Loading...