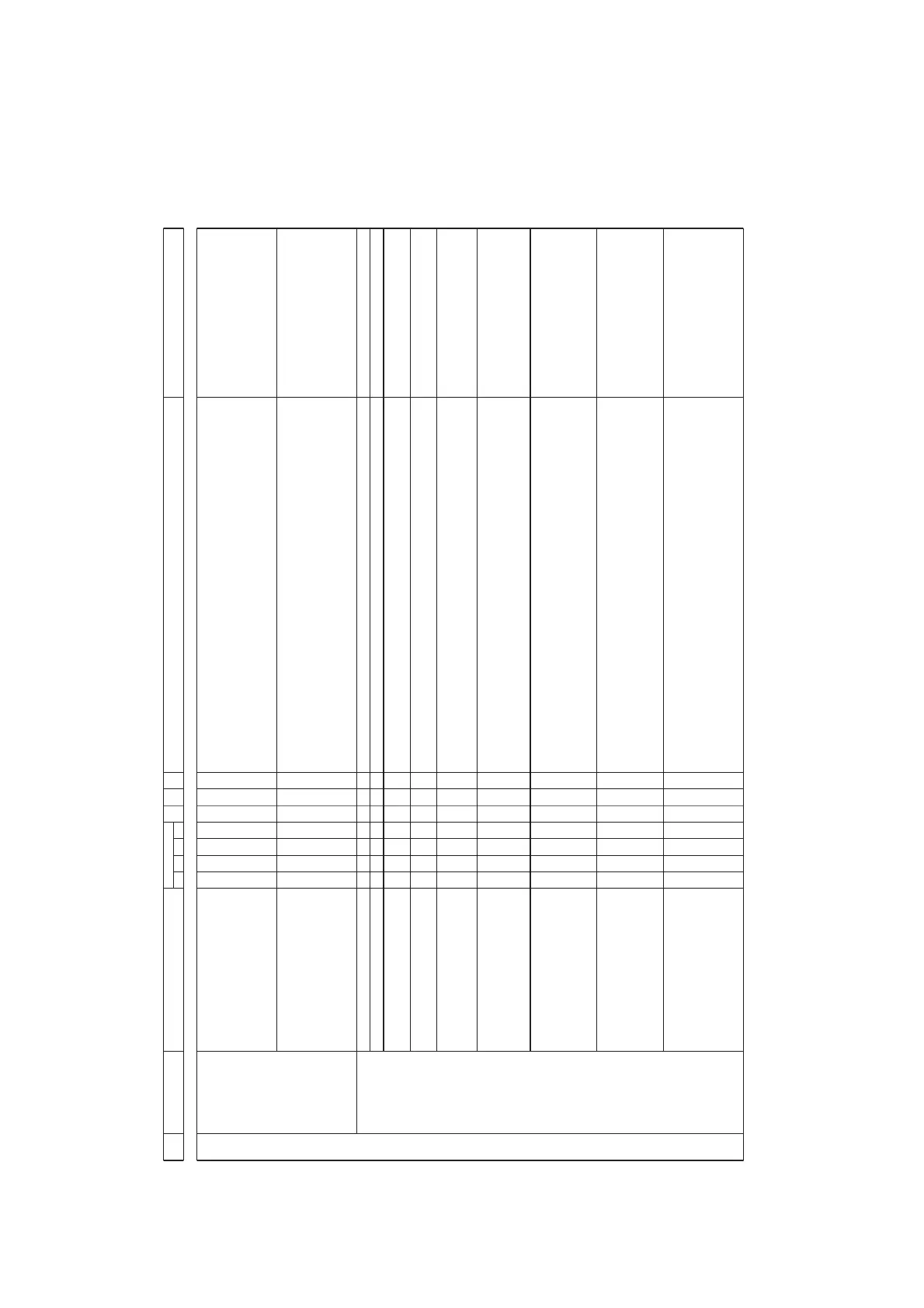

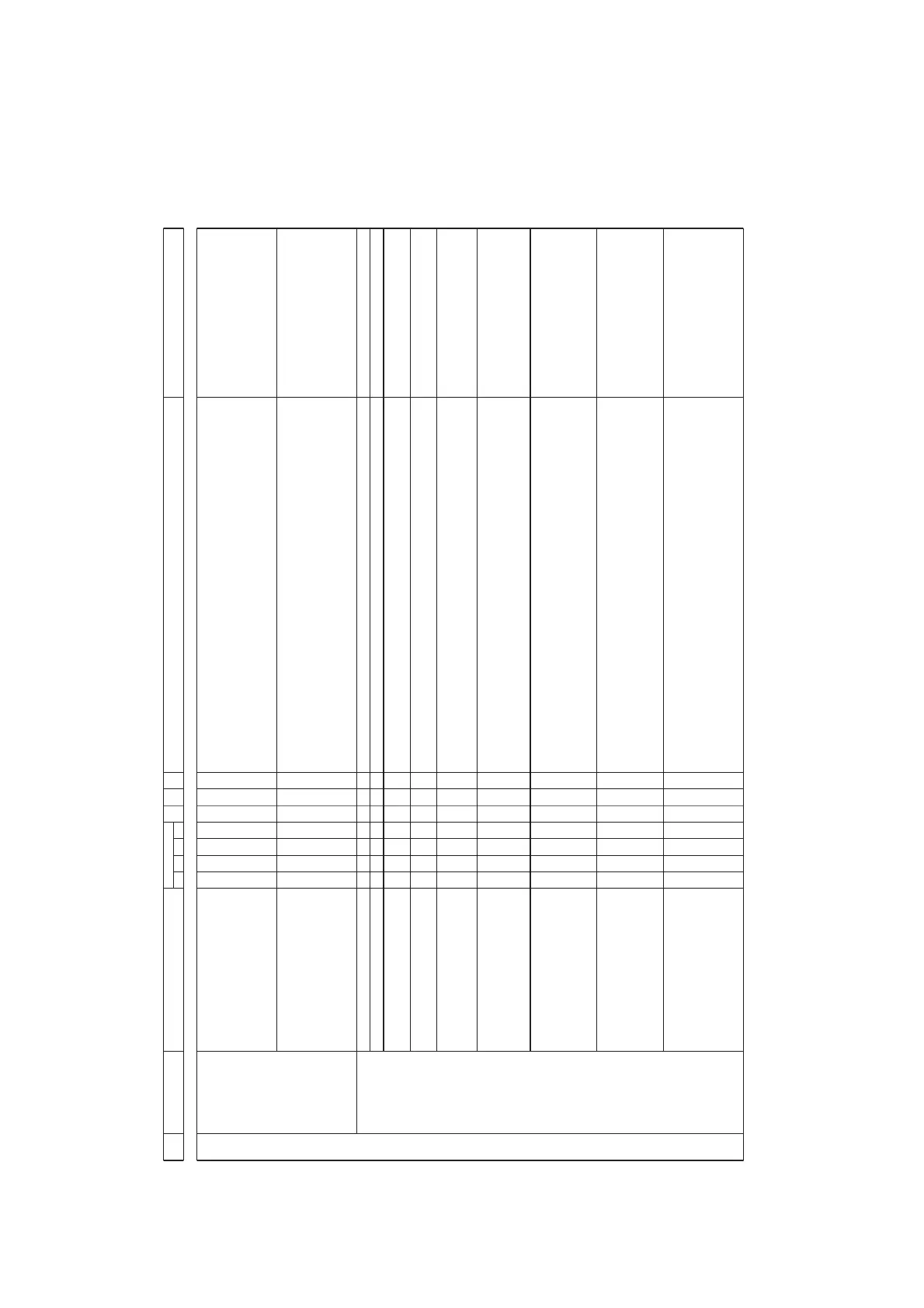

Chapter 16

Appendix

Instruction Set XVI - 11

MOVM (SP),[reg1,.,regn]

MOVM [reg1,.,regn],(SP)

mem32(SP+40)→reg1,mem32(SP+36)→reg2,

mem32(SP+32)→reg3,mem32(SP+28)→D0,

mem32(SP+24)→D1,mem32(SP+20)→A0,

mem32(SP+16)→A1,mem32(SP+12)→MDR,

mem32(SP+8)→LIR,mem32(SP+4)→LAR,

SP+44→SP

mem32(SP+44)→D2,mem32(SP+40)→D3,

mem32(SP+36)→A2,mem32(SP+32)→A3,

mem32(SP+28)→D0,mem32(SP+24)→D1,

mem32(SP+20)→A0,mem32(SP+16)→A1,

mem32(SP+12)→MDR,mem32(SP+8)→LIR,

mem32(SP+4)→LAR,SP+48→SP

PC+2→PC

reg→mem32(SP-4),SP-4→SP

reg1→mem32(SP-4),reg2→mem32(SP-8),

SP-8→SP

reg1→mem32(SP-4),reg2→mem32(SP-8),

reg3→mem32(SP-12),SP-12→SP

D2→mem32(SP-4),D3→mem32(SP-8),

A2→mem32(SP-12),A3→mem32(SP-16),

SP-16→SP

D0→mem32(SP-4),D1→mem32(SP-8),

A0→mem32(SP-12),A1→mem32(SP-16),

MDR→mem32(SP-20),LIR→mem32(SP-24),

LAR→mem32(SP-28),SP-32→SP

reg→mem32(SP-4),D0→mem32(SP-8),

D1→mem32(SP-12),A0→mem32(SP-16),

A1→mem32(SP-20),MDR→mem32(SP-24),

LIR→mem32(SP-28),LAR→mem32(SP-32),

SP-36→SP

reg1→mem32(SP-4),reg2→mem32(SP-8),

D0→mem32(SP-12),D1→mem32(SP-16),

A0→mem32(SP-20),A1→mem32(SP-24),

MDR→mem32(SP-28),LIR→mem32(SP-32),

LAR→mem32(SP-36),SP-40→SP

reg1→mem32(SP-4),reg2→mem32(SP-8),

reg3→mem32(SP-12),D0→mem32(SP-16),

D1→mem32(SP-20),A0→mem32(SP-24),

A1→mem32(SP-28),MDR→mem32(SP-32),

LIR→mem32(SP-36),LAR→mem32(SP-40),,

SP-44→SP

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

2

2

2

2

2

2

2

2

2

2

2

11

12

1

1

2

3

4

8

9

10

11

S1

S1

1

1100

1100

2

1110

1111

3

<regs

<regs

4

....>

....>

56

Group

Mnemonic

Operation

Machine Code

Notes

Flag

Code

Size

Cycle

For

-mat

MN1030/MN103S SERIES INSTRUCTION SET

789

10

11

12

13 14

VF

CF NF

ZF

MOVM

registers specified with regs=10(*1)

rregisters specified with regs=11

registers specified with regs =0

registers specified with regs=1

registers specified with regs= 2(*2)

registers specified with regs= 3(*2)

registers specified with regs= 4

registers specified with regs= 7

registers specified with regs= 8(*2)

registers specified with regs= 9(*2)

registers specified with regs= 10(*2)

*1: Registers specified with regn are returned in the order; D2, D3, A2 and A3 no matter when the assembler writes theses

registers. Skip the registers which is not specified

*2: Registers specified with regn are saved in the order; D2, D3, A2 and A3 no matter when the assembler write these

registers. Skip the registers which is not specified.

Loading...

Loading...