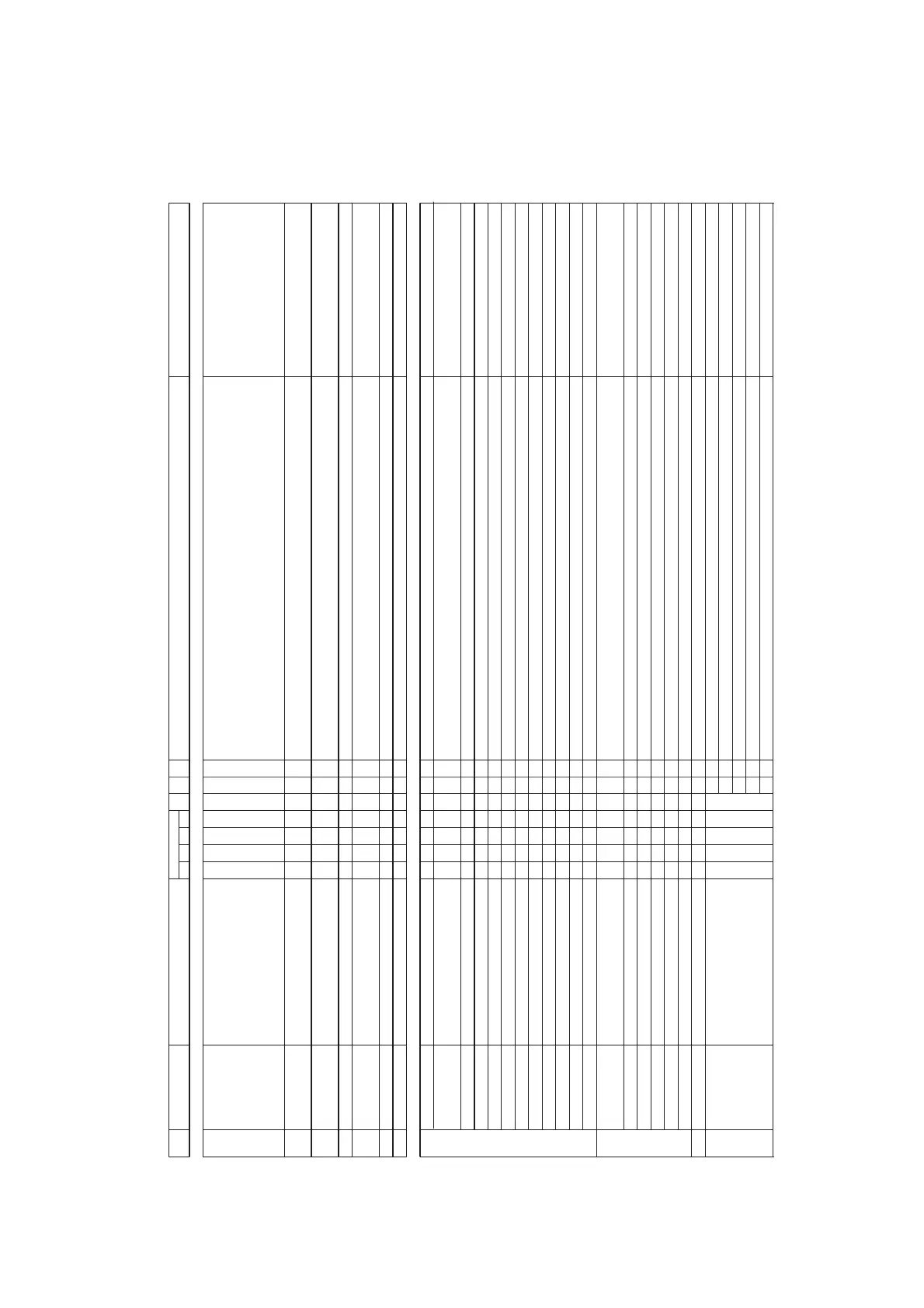

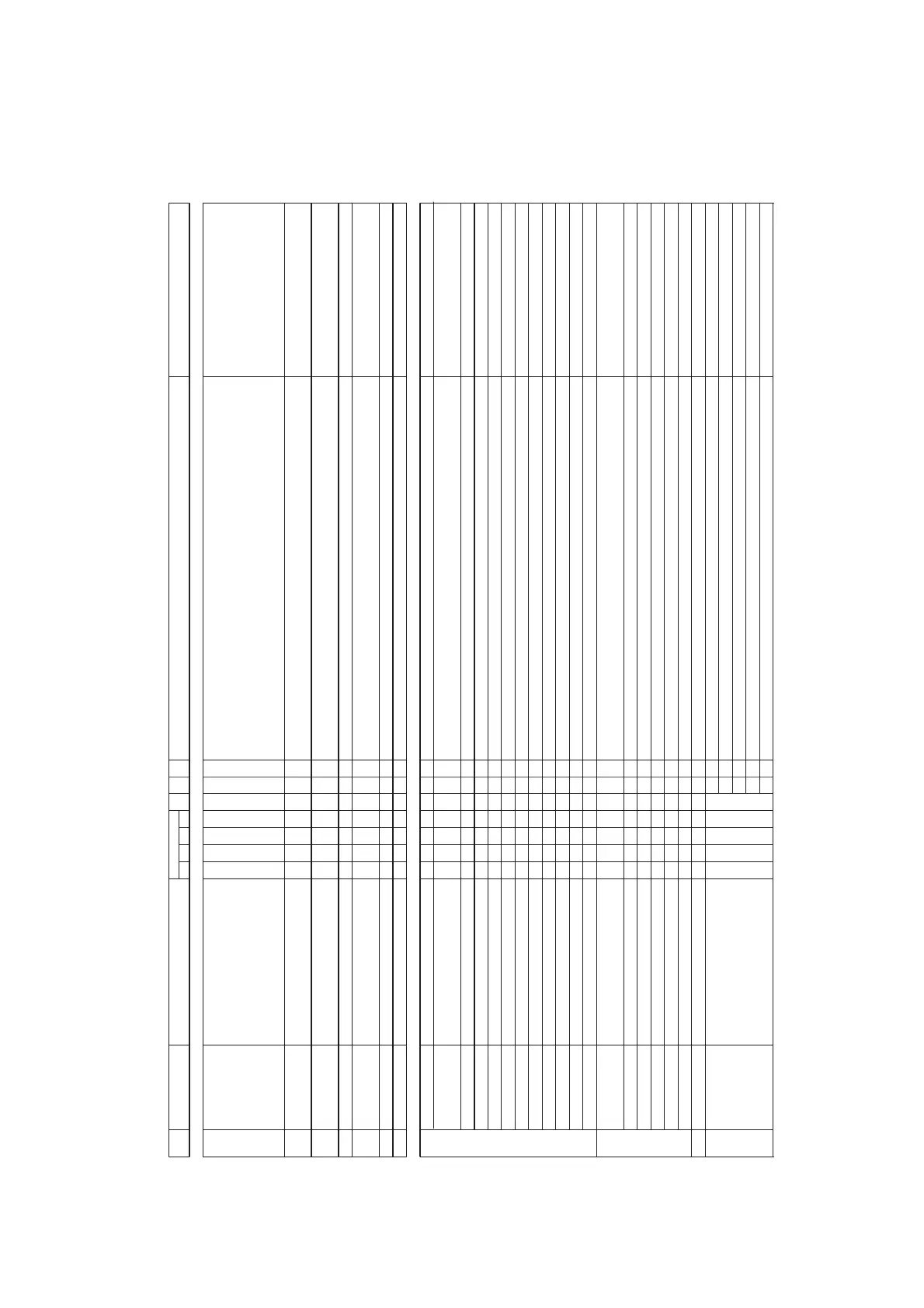

Chapter 16

Appendix

XVI - 12 Instruction Set

MOVM regs,(SP)

EXT Dn

EXTB Dn

EXTBU Dn

EXTH Dn

EXTHU Dn

CLR Dn

ADD Dm,Dn

ADD Dm,An

ADD Am,Dn

ADD Am,An

ADD imm8,Dn

ADD imm16,Dn

ADD imm32,Dn

ADD imm8,An

ADD imm16,An

ADD imm32,An

ADD imm8,SP

ADD imm16,SP

ADD imm32,SP

ADDC Dm,Dn

SUB Dm,Dn

SUB Dm,An

SUB Am,Dn

SUB Am,An

SUB imm32,Dn

SUB imm32,An

SUBC Dm,Dn

MUL Dm,Dn

D2 → mem32(SP-4),D3 → mem32(SP-8)

A2 → mem32(SP-12),A3 → mem32(SP-16)

D0 → mem32(SP-20),D1 → mem32(SP-24)

A0 → mem32(SP-28),A1 → mem32(SP-32)

MDR → mem32(SP-36),LIR → mem32(SP-40)

LAR → mem32(SP-44),SP-48 → SP

IF (Dn.bp31=0), 0x00000000 → MDR

IF (Dn.bp31=1), 0xFFFFFFFF → MDR

IF (Dn.bp7=0), Dn & 0x000000FF → Dn

IF (Dn.bp7=1), Dn | 0xFFFFFF00 → Dn

Dn & 0x000000FF → Dn

IF (Dn.bp15=0), Dn & 0x0000FFFF → Dn

IF (Dn.bp15=1), Dn | 0xFFFF0000 → Dn

Dn & 0x0000FFFF → Dn

0 → Dn

Dm + Dn → Dn

Dm + An → An

Am + Dn → Dn

Am + An → An

imm8(sign_ext) + Dn → Dn

imm16(sign_ext) + Dn → Dn

imm32 + Dn → Dn

imm8(sign_ext) + An → An

imm16(sign_ext) + An → An

imm32 + An → An

imm8(sign_ext) + SP → SP

imm16(sign_ext) + SP → SP

imm32 + SP → SP

Dm + Dn + CF → Dn

Dn - Dm → Dn

An - Dm → An

Dn - Am → Dn

An - Am → An

Dn - imm32 → Dn

An - imm32 → An

Dn - Dm - CF → Dn

(Dn* Dn) → { MDR , Dn }

-

-

-

-

-

-

0

z

z

z

z

z

z

z

z

z

z

-

-

-

z

z

z

z

z

z

z

z

?

-

-

-

-

-

-

0

z

z

z

z

z

z

z

z

z

z

-

-

-

z

z

z

z

z

z

z

z

?

-

-

-

-

-

-

0

z

z

z

z

z

z

z

z

z

z

-

-

-

z

z

z

z

z

z

z

z

z

-

-

-

-

-

-

1

z

z

z

z

z

z

z

z

z

z

-

-

-

z

z

z

z

z

z

z

z

z

2

2

1

1

1

1

1

1

2

2

2

2

4

6

2

4

6

3

4

6

2

2

2

2

2

6

6

2

2

12

1

1

1

1

1

1

1

1

1

1

1

1

2

1

1

2

1

1

2

1

1

1

1

1

2

2

1

3

13

21

29

34

S1

D0

S0

S0

S0

S0

S0

S0

D0

D0

D0

S1

D2

D4

S1

D2

D4

D1

D2

D4

D0

D0

D0

D0

D0

D4

D4

D0

D0

1

1100

1111

0001

0001

0001

0001

0000

1110

1111

1111

1111

0010

1111

1111

0010

1111

1111

1111

1111

1111

1111

1111

1111

1111

1111

1111

1111

1111

1111

2

1111

0010

00Dn

01Dn

10Dn

11Dn

Dn00

DmDn

0001

0001

0001

10Dn

1010

1100

00An

1010

1100

1000

1010

1100

0001

0001

0001

0001

0001

1100

1100

0001

0010

3

<regs

1101

0101

0110

0111

<imm8

1100

1100

<imm8

1101

1101

1111

1111

1111

0100

0000

0010

0001

0011

1100

1101

1000

0100

4

....>

00Dn

AmDn

DmAn

AmAn

....>

00Dn

00Dn

....>

00An

00An

1110

1110

1110

DmDn

DmDn

DmAn

AmDn

AmAn

10Dn

01An

DmDn

DmDn

5

<imm16

<imm32

<imm16

<imm32

<imm8

<imm16

<imm32

<imm32....

<imm32....

6

....

....

....

....

....>

....

....

Group

Mnemonic

Operation

Machine Code

Notes

Flag

Code

Size

Cycle

For

-mat

MN1030/MN103S SERIES INSTRUCTION SET

7

....

....

....

....

....

....

....

....

8

....>

....

....>

....

....>

....

....

....

9

....

....

....

....

....

10

....

....

....

....

....

11

....

....

....

....

....

12

....>

....>

....>

....>

....>

13 14

VF

CF NF

ZF

MOVM

EXT

EXTB

EXTBU

EXTH

EXTHU

CLR

Arithmetic Operation Instructions

ADD

ADDC

SUB

SUBC

MUL

Registers specified with regs =11

Dn =0

Dn =value by 1 byte

Dn =value by 2-byte

Dn =value by 3-byte

Dn =value by 4-byte

Loading...

Loading...